Defense & Aerospace

Proven Performance for Mission-Critical Testing

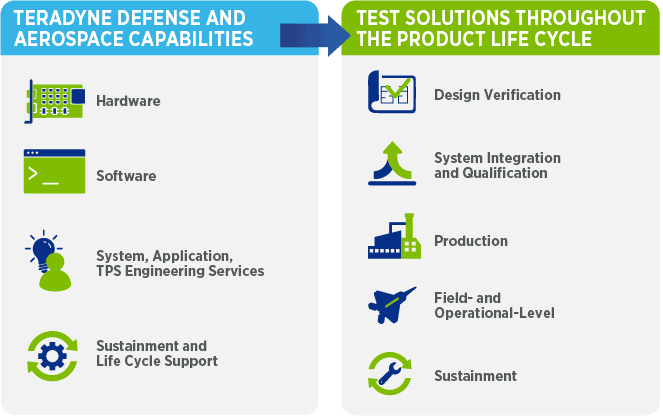

Deployed in over one hundred Defense and Aerospace programs for over four decades, Teradyne’s innovative automatic test solutions continue to provide leading-edge capability, exceptional reliability, and world-class services to military facilities and manufacturers worldwide.

Unmatched Expertise and Long-term Commitment

Teradyne’s Defense and Aerospace products are designed to serve all levels of ATE deployment. Our software-defined modular instruments address rapidly evolving test requirements and equipment obsolescence. The scalable Spectrum Systems cover test applications from lab-focused, to production and depot test. Teradyne also has extensive experience to provide complete test solutions, engineering services and sustainment support required for successful long-term deployment.

Dependable Test Solutions for the Product Life Cycle

Design Verification, System Integration, & Qualification Test Solutions

Teradyne offers a variety of solutions suitable for product design verification, Hardware-in-the-Loop (HIL) simulation, and system-level qualification. Our system test, integration, and flight test tools help lower costs and risks, and reduce time to market for new aircraft, vehicle or shipboard systems.

Learn more about Teradyne’s design, simulation, and qualification offerings

Production Functional Test Solutions

Achieving repeatable, scalable manufacturing is a complex task, often impacted by technical challenges and limited resources. Teradyne has the capability to deliver complete test solutions that minimize the time to set up new product manufacturing process at a defined cost and schedule.

Learn more about Teradyne’s Total Test Solution for the Factory

Depot-Level, Intermediate-Level, and Operational-Level Test Solutions

Teradyne’s offers cost-effective, modular, open-architecture test solutions for all levels of maintenance that ensure mission-readiness of defense and aerospace electronics while supporting interoperability and standardization of today’s most advanced Automatic Test Systems (ATS) programs.

Learn more about Teradyne’s D-level, I-level, and O-level test solutions

Test Equipment Sustainment, Logistics, and Life Cycle Support

Managing long-term sustainment of test equipment not only involves maintenance and repair, but also configuration, obsolescence management, and technology updates. Teradyne’s Total Support Solution enables customers to improve uptime and manage obsolescence throughout their ATE life cycle.

Learn more about Teradyne’s Sustainment, Logistics, and Life-cycle Support

Ground Maintenance and Operations

Minimize aircraft downtime and maintenance costs. Teradyne offers ground support equipment solutions including portable data loaders, aircraft system monitoring, and fleet management tools that are reliable, easy to use, and low maintenance.

Learn more about Teradyne’s ground maintenance and operation support solutions.