邁向測試之路

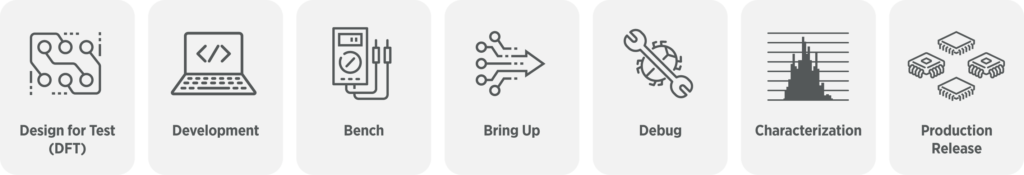

將積體電路(IC)從設計階段推進至測試階段,是一個艱鉅的過程,涵蓋了多個步驟,包括:

- 可測試性設計(DFT):確保晶片設計方式能使其可供測試的流程

- 開發:自動化測試程式(ATP)的開發

- 實驗台測試:在實驗台上對設備進行評估,以確保設計正確且符合所需規格

- 執行:將已開發的測試移至自動化測試設備(ATE)

- 除錯:在 ATE 上除錯測試

- 特性分析:確定製作上的差異;並針對表現、音量、時機等進行微調。

- 生產版本發布:將 ATP 移至完整生產環境進行大規模測試

這是一個迭代過程,可能需要數月時間,因此應評估每個步驟,以確定能否在整個過程中實現效率提升。任何步驟中的微小改進都可能影響其他步驟,並大幅縮短整體週期時間。

漫長而艱辛的開發與除錯過程

其中一個效率明顯低下的環節,在於將測試程式從開發階段移轉至生產環境所需的時間,尤其是除錯過程。

設計工程師與測試台工程師使用同一套工具來建立測試序列,這些序列的抽象層級比測試工程師所使用的測試更高。測試工程師在操作自動測試設備(ATE)時,通常處於更低的層級,涉及電平與時序等細節,且其操作的向量僅由一和零組成;因此,測試工程師與設計工程師所使用的工具之間存在語言隔閡,這使得除錯工作變得更加複雜。

讓我們來看看目前現行的流程。

測試程式的開發需要時間,而且需要大量時間

在最高層級,設計工程師與測試台工程師所使用的工具,能夠以一般自動測試設備(ATE)無法提供的形式與裝置進行通訊。這些工具所使用的語言、裝置的原生環境,以及自動測試設備(ATE)所採用的格式之間,存在著落差。讓我們來看看一個具體的例子。

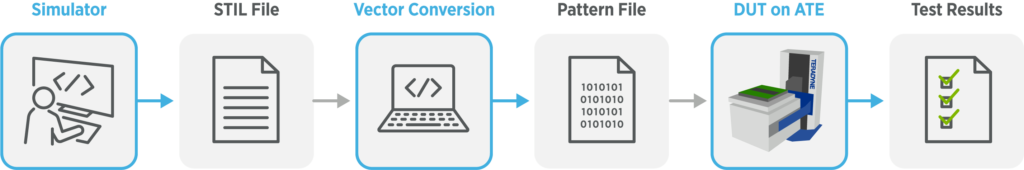

在典型的圖案流程中,模擬器會輸出例如 STIL 或 WGL 檔案,這些檔案會由圖案轉換器轉換為圖案。這些圖案隨後被載入至測試機中,以便在自動測試設備(ATE)上執行,對裝置進行測試(該裝置稱為被測裝置,即 DUT)。

若遇到問題,自動測試設備(ATE)僅會提供「通過/未通過」的結果,卻不會提供任何關於問題成因的資訊。此時,測試工程師必須從資料日誌中擷取大量數據,並將這些資訊轉交給設計或實驗台工程師;然而,這些工程師收到的數據格式往往是他們不熟悉的。因此,必須將這些數據轉換成他們能理解的結果,才能在模擬環境中重現該問題。

一旦問題被確認,設計工程師便可修改程式碼並為測試工程師生成一組新的輸入資料;隨後,這些資料必須轉譯回平面圖樣,以便在自動測試設備(ATE)上再次執行測試,以確認問題是否已解決。每次這樣的來回轉換都需要耗費時間,且可能引發更多問題,甚至導致回歸問題。

此外,設計工程師與測試工程師通常不會同時進行工作,這導致回應之間產生時間差,並使本已耗時的流程更加延遲。要取得一套合適的測試方案,可能需要數週,甚至數月之久。

那麼,我們該如何縮短除錯時間呢?答案是讓測試工程師能夠以更高的抽象層級進行溝通,使測試工程師與設計工程師能夠使用相同的語言交流。

簡化流程

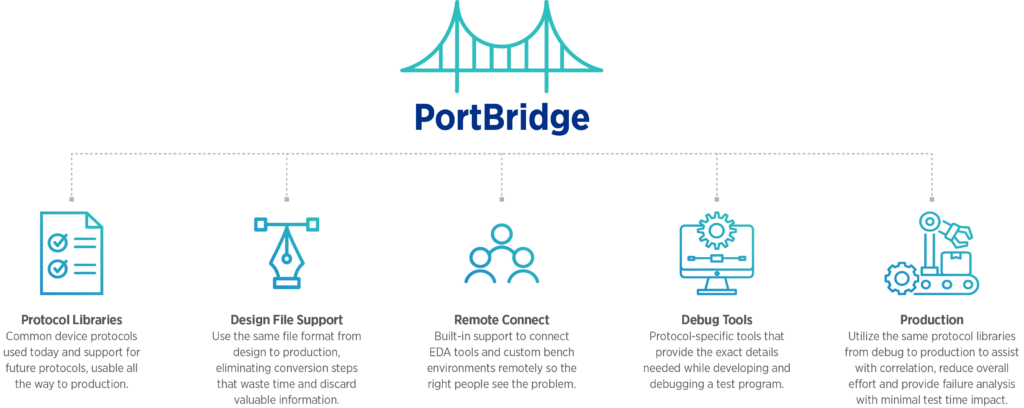

為了促進這種簡化的資訊流動,泰瑞達開發了 PortBridge 工具,讓設計工程師和實驗台工程師能夠直接與自動測試設備(ATE)通訊以進行除錯,同時也讓測試工程師能夠理解並診斷平面圖中的故障。

PortBridge 與泰瑞達的 UltraFLEXplus 及UltraFLEX測試機,並提供:

- 涵蓋當今裝置所使用的常見通訊協定,以及未來所需的通訊協定之函式庫。可直接用於量產。

- 「遠端連線」功能內建支援,可將 EDA 工具及自訂測試平台環境遠端連接到 ATE。讓合適的人員使用他們熟悉的工具和環境來處理問題。

- 設計檔案支援功能,可支援標準設計格式(如 SVF)或自訂格式,從而省去耗時且易導致重要資訊遺失的轉換步驟

- 主機除錯工具,提供開箱即用的、針對特定通訊協定的工具,能在開發和除錯測試程式時,精確呈現所需的詳細資訊

- 生產環境支援:從除錯到生產環境皆可使用相同的協定函式庫,有助於關聯分析、減少整體工作量,並在最佳測試時間內提供故障分析。

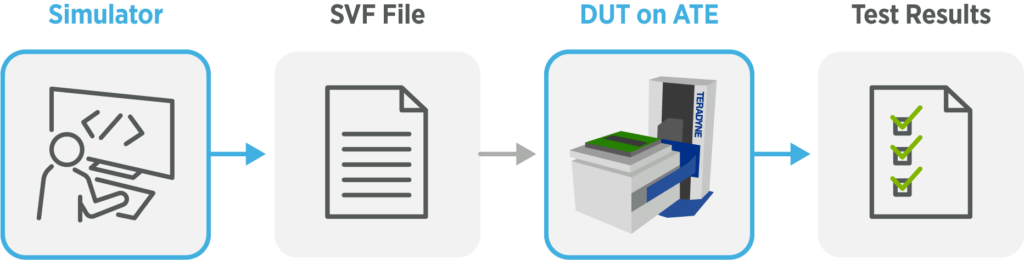

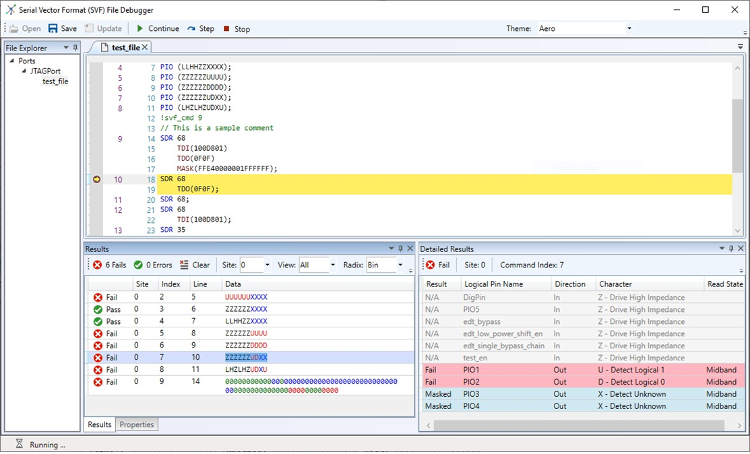

上圖以 PortBridge 及序列向量格式 (SVF) 檔案為例,展示了一個典型的流程。SVF 檔案是一種業界標準,用於以 ASCII(文字)檔案格式表示 JTAG 測試模式。

SVF 檔案的優勢在於,它是一種包含註解的簡化程式碼檔。測試工程師和設計工程師希望直接在寄存器中進行操作,而非處理平面程式碼檔——在平面程式碼檔中,200 條指令可能會轉化為數千甚至數萬行程式碼。SVF 檔案提供了一種簡化的平面程式碼檔,其中註解直接嵌入程式碼中,因此當發生錯誤時,可透過註解輕鬆理解這些程式碼行的含義。

透過 PortBridge,模擬器輸出的 SVF 檔案可直接在 ATE 上執行,無需使用 ATPG。可透過內嵌註解來理解並診斷故障,且可在 ATE 上直接進行除錯。這省去了將平面波形轉換為設計工程師能理解的格式以便除錯,然後再將檔案轉換回平面波形以在 ATE 上執行的步驟。 此除錯工具不僅具備功能齊全的除錯器所應有的所有標準功能,還允許設定陷阱並即時檢視結果。

若裝置發生問題,PortBridge 可讓 ATE 與 EDA 工具或測試台腳本之間建立直接通訊。 在測試機上所做的變更會即時反映,且任何已連接的工具皆可遠端查看裝置的狀態。這使設計與測試平台工程師能夠使用自己最熟悉的工具,同時與測試工程師協作,直接在 ATE 上對被測裝置 (DUT) 進行除錯。相較於修改並重新轉換更新的 STIL 或 WGL 檔案,此流程可節省大量時間。

結論

從測試設計過渡到量產是一個耗時的過程,其中許多步驟都可能引入錯誤,但 PortBridge 能夠簡化這個流程。 透過在更高抽象層級進行程式設計與除錯來降低複雜度,意味著設計、DFT(可測試性設計)與測試工程團隊之間的溝通將減少翻譯問題與延遲。借助 PortBridge,憑藉其針對平台與軟體進行優化的解決方案,除錯時間可從數月縮短至數日。在未來的文章中,我們將透過實際應用案例,展示 PortBridge 如何被運用來最大限度地減少除錯時間與工作量。

請聯絡我們,了解如何在您的 UltraFLEXplus 或UltraFLEX測試機上運用 Teradyne 的 PortBridge 工具,以簡化從設計到測試的流程。

理查德·范寧 是泰瑞達(Teradyne)的首席軟體工程師,負責領導 PortBridge 軟體計畫。 在此職位之前,他曾主導 HexVS 儀器板及特性分析 API 與 GUI 改進專案的軟體開發,並在 IG-XL 中架構了 Protocol Aware 解決方案,此外還參與了針對 FLEX、UltraFLEX 及UltraFLEXplus 眾多其他儀器與軟體專案。理查德自 2000 年從哈維穆德學院畢業後便一直任職於泰瑞達。

約翰·羅(John Rowe)在泰瑞達(Teradyne)擔任工廠應用工程師一職已逾 20 年,主要負責 PortBridge 軟體以及設計、測試台與自動測試設備(ATE)的整合工作。在加入泰瑞達工廠應用部門之前,約翰曾在德克薩斯州擔任現場應用工程師。