首頁 | 泰瑞達 PortBridge 協助 Marvell 提升測試工程生產力

← 返回

將積體電路(IC)從設計階段推進至測試階段,是一個涵蓋眾多步驟的艱鉅過程。這是一個可能耗時數月的迭代過程;隨著產品上市週期不斷縮短,工程團隊如今被要求在過去僅需管理單一晶片的時間框架內,同時支援多項晶片設計——有時甚至多達五、六項新設計。 當然,他們首先會自問:如何在資源相同或更少的情況下,於更短的時間內完成更多工作?

其中一個效率低下的關鍵環節,在於將測試程式從開發階段移轉至生產階段所需的時間,尤其是除錯過程。設計工程師與測試台工程師使用一套工具來建立測試序列,而操作自動測試設備(ATE)的測試工程師,通常則在更底層的層級與時序層面上進行操作,其資料向量由一和零組成;因此,測試工程師與設計工程師所使用的工具之間存在語言隔閡,這使得除錯工作變得更加複雜。 若能在此流程的任何環節進行微小改進,便能大幅縮短整體週期時間。

挑戰

在Marvell——這家專為人工智慧、雲端運算、汽車及連網裝置提供複雜系統單晶片(SoC)的領先供應商——市場上市週期不斷縮短,裝置規格要求日益提高,而可接受的缺陷率則已逼近可忽略不計的水平。該公司正尋求一套解決方案,以優化從設計到測試的流程,確保裝置在啟動階段及進入大量量產時能達到最高效率。透過泰瑞達(Teradyne)的 PortBridge,他們找到了實用的解決方案,協助其滿足這些嚴苛的要求。

泰瑞達的解決方案

採用 PortBridge 後,Marvell 很快便感受到工作流程的改善。相較於自行開發通訊協定函式庫,PortBridge 讓他們在每個所需通訊協定的非重複性工程(NRE)上節省了 3 至 5 週的時間。由於這些函式庫是現成商用產品的一部分,因此已完全經過優化,且持續維護成本也隨之降低。省下這部分基礎架構工作的心力,讓團隊得以專注於實作特定裝置的測試程式碼。

PortBridge 測試檔案支援功能將這些生產力提升推向更高境界。透過將基於協定的測試抽象化為簡潔的檔案,供測試程式直接讀取並執行,這進一步減少了支援新裝置所需的裝置專屬程式碼。Marvell 開發了基於 SVF 的測試檔案與測試程式範本,以實現快速的程式開發。透過此基於範本的工作流程,他們成功將支援新設計所需的時間從數週縮短至數天。

除了測試程式開發成本之外,針對新設計進行除錯往往相當耗時。 以某個案例為例,Marvell 在一款高複雜度的 5 奈米設計中遭遇初期問題,且無法透過現有的測試程式診斷出問題所在。團隊成功讓設計團隊利用他們所建立的 SVF 範本,迅速建立客製化的診斷測試,並得以快速找出問題的根本原因。相較於以往的模式除錯工作流程,團隊估計此舉為他們節省了約 6 至 8 週的時間。

解決方案的優勢

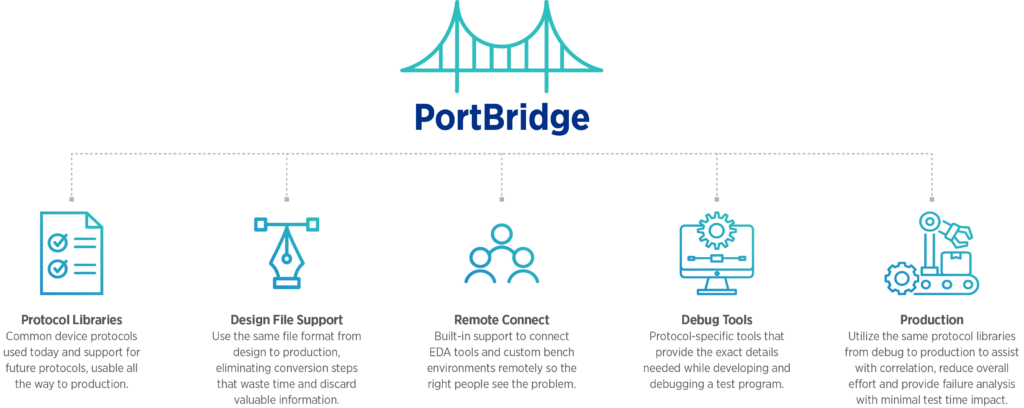

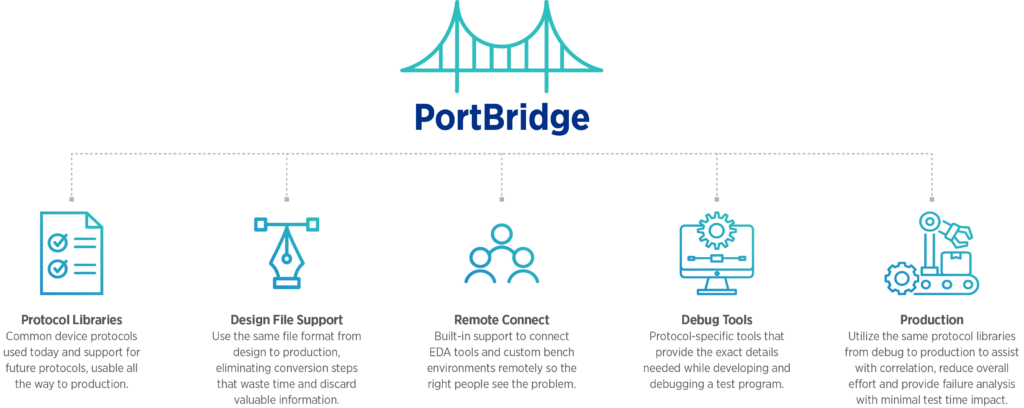

泰瑞達(Teradyne)的 PortBridge 讓測試工程師與設計工程師能夠使用相同的語言溝通。透過 PortBridge,設計工程師與測試台工程師可直接與自動測試設備(ATE)進行通訊,以進行除錯與故障診斷。 透過設計工具中的內嵌註解,可理解並診斷故障,且能直接在 ATE 上進行除錯。這省去了將平面波形轉換為設計工程師能理解的格式以便除錯,再將檔案轉換回平面波形以在 ATE 上執行的步驟。PortBridge 可與泰瑞達的 UltraFLEXplus 及

UltraFLEX測試機,並提供:

- 涵蓋當今裝置所使用的常見通訊協定,以及未來所需的通訊協定之函式庫。

- 「遠端連線」功能,可將 EDA 工具及自訂測試平台環境遠端連接到 ATE。

- 支援設計檔案,可使用標準或自訂格式,省去轉換步驟。

- 主機除錯工具, 這是一組針對特定通訊協定的 工具,可提供開發與除錯過程中所需的精確細節。

- 生產環境支援:從除錯到生產環境,請使用相同的通訊協定函式庫,以便進行關聯性分析與故障分析。

部署