在受立法、技術發展及人才市場變動影響的環境中,測試主管扮演著至關重要的角色

半導體產業正經歷急速變革,政府對產能回流的支持,在亞洲、美國和歐洲的資源之間催生了新的互動關係——即便在此同時,該產業仍在開發並維持 HBM 和異質整合等新技術。 諸如《美國半導體生產激勵法案》(CHIPS Act)、專業工程師短缺,以及與人工智慧相關的新效能需求等地緣政治因素,皆加劇了產業面臨的挑戰並推動其快速演進。

這對半導體測試意味著什麼?自動化測試設備(ATE)廠商正透過調整技術、提升自動化程度,並與半導體製造商密切合作,在應對這些挑戰方面發揮著關鍵作用。測試資源已被證實至關重要,它確保了該產業能夠持續創新,並滿足全球市場日益增長的需求。

地緣政治與半導體產業的影響

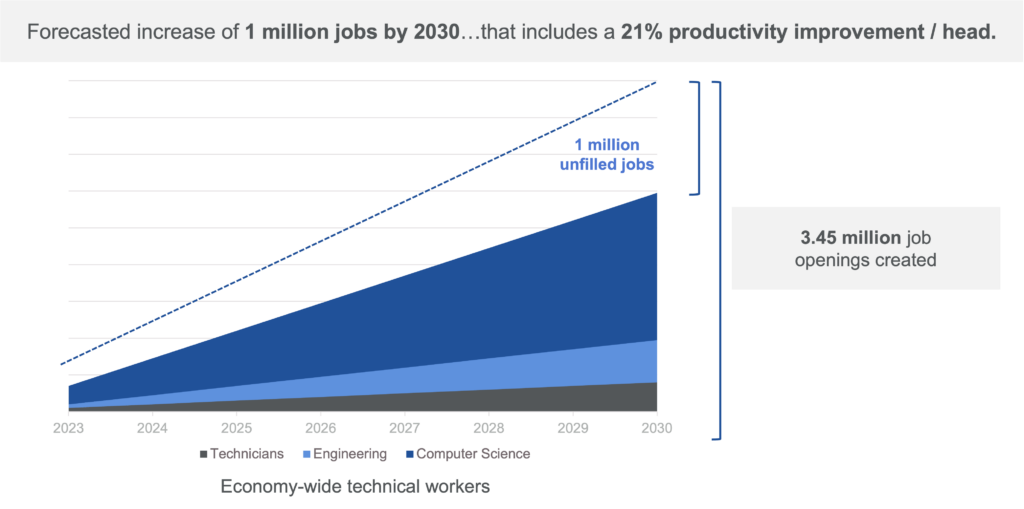

半導體市場正經歷變革,各國政府正致力將製造產能回流至美國與歐洲。《美國晶片法案》(CHIPS Act)是一項旨在強化國內半導體製造與研發的重要立法措施。該法案提供的龐大資金與激勵措施,旨在解決供應鏈中斷及地緣政治緊張局勢所暴露的脆弱性。 這筆資金亦用於支持人才培育,因為美國面臨產業人才短缺問題,預計未來幾年將短缺 7 萬至 9 萬名從業人員;即使生產力有所提升,到 2030 年全球仍將有超過 100 萬個職位無法填補。

《晶片法案》亦為半導體技術的先進研究提供資金——這促使業界亟需在半導體測試方法與尖端測試設備方面進行創新。隨著測試領域不斷演進,以應對具備先進封裝與異質整合技術的晶片所帶來的複雜性,此舉至關重要,有助於確保該產業能充分準備,以滿足人工智慧與高效能運算所帶來的廣泛需求。

歐洲和亞洲也正在推行類似的計畫,各方皆致力於強化自身基礎設施。各區域之間的互動關係相當複雜:儘管美國和歐洲正大力投資於自身的半導體生態系統,亞洲——尤其是台灣和南韓——仍舊是半導體製造領域的強權。

《晶片法案》(CHIPS Act)對測試產業的影響深遠。資金的湧入正提升半導體的生產能力,進而帶動對測試設備與服務的需求。隨著美國境內新建晶圓廠與封裝廠,國內半導體測試資源的需求也隨之增加。

測試領域的新需求與新機遇

這些由政府支持的基礎設施投資,正值半導體設計、開發與測試領域的關鍵時刻。隨著人工智慧的發展,人們對先進數位晶片的性能與可靠性愈發重視——全球對那些需要超高速性能、但同時伴隨著更高複雜度與功耗需求的應用,需求正持續攀升。

隨著半導體製程節點不斷縮小(例如低於 5 奈米製程),確保其性能、可靠性和功耗效率的複雜度也呈指數級增長。微型化每向前邁進一步,便會在製造精度、熱管理及缺陷檢測方面帶來新的挑戰。技術的進步增加了對所有晶圓廠設備的整體壓力,其中包括製造商所依賴的自動測試設備(ATE)系統——這些系統直接影響最終的晶片良率,而良率最終將轉化為營收。

眾所周知,透過縮小半導體製程節點來提升效能的時代已趨緩,為維持摩爾定律的發展軌跡,必須在設計、材料及封裝方面進行創新。 晶片製造商正採用先進封裝技術以滿足所需的處理速度,包括多顆異質整合的半導體晶片(chiplets)以及 2.5D/3D 封裝結構。這使得晶圓廠在可靠生產「已知良品晶片」(KGD)與「已知良品中介層」(KGI)方面面臨更大壓力,進而導致在將單一晶片組裝成更大系統之前,必須採用日益精細的測試方法來驗證其性能與可靠性。

自動測試設備 (ATE) 產業正積極因應日益複雜的交匯因素

泰瑞達致力於走在這些需求的前端,確保全球半導體生態系統在面臨前所未有的挑戰時,仍能持續創新並蓬勃發展。

為因應全球半導體產業的劇烈變革,該公司已採行一套靈活的測試策略。這包括能在製造流程中靈活調整測試時機,以有效管控品質成本。早期測試可將報廢成本降至最低,而後期測試則能確保品質控制的徹底性。這是一種平衡的策略,能在整個測試過程中維持品質,同時善用數據分析、降低成本並提升良率。

關於「左移」與「右移」的更多資訊

2.5D/3D 封裝技術確實推動了摩爾定律的進展,但其經濟可行性取決於能否在製造初期降低缺陷滲透率(即最終進入量產階段的缺陷數量),從而降低報廢成本。在製程中將測試環節向左或向右移,有助於實現此目標並將整體成本降至最低。

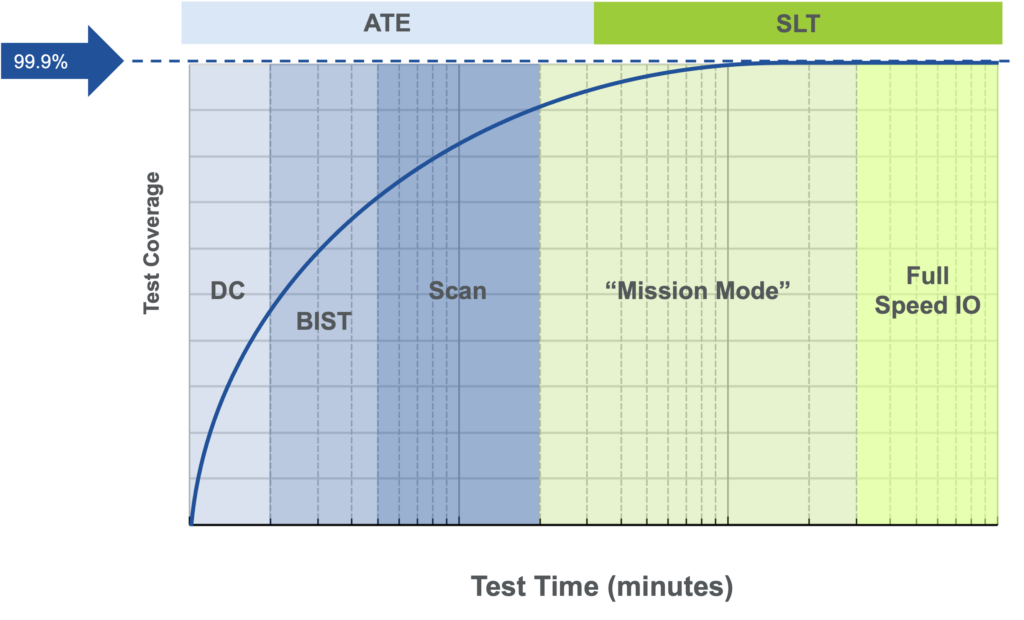

在早期階段提高測試覆蓋率被稱為「左移」,此過程發生於晶圓檢測及部分封裝階段,旨在最大化「可接受的良率」(KGD),從而有助於降低未來的封裝成本。然而,此舉可能會增加測試成本,因此必須權衡其與減少報廢率的效益。

「右移」策略旨在於開發流程的後期階段提升測試覆蓋率,以偵測缺陷並維持品質。此方法透過在最終(或系統層級)測試中採用更高的並行度,在達成品質目標的同時降低成本。高產出測試可移至這些後期階段,以優化效率。

目標是在整個製造過程中平衡品質與良率,從而優化整體成本。相關策略包括透過降低晶圓測試中的瑕疵漏檢率來減少報廢成本,以及高效執行量產測試以降低測試成本。最終,在動態且持續的流程中,分析技術將為「左移」或「右移」的決策提供依據。藉由掌握寶貴的數據,可在晶片製造的各個階段調整測試策略,建立一個閉環改進機制,在提升良率的同時將測試成本降至最低。

靈活的測試策略應對挑戰

當今動態的測試覆蓋率亦結合了自動測試設備(ATE),例如泰瑞達的 UltraFLEXplus等system level test (SLT)ATE),並system level test (SLT),後者可透過泰瑞達的Titan 平台執行。系統級測試能模擬真實環境條件,以最佳化整合式半導體元件的驗證流程,對於系統單晶片(SoC)和系統級封裝(SiP)等先進技術尤為實用,能有效識別故障、控制成本,並透過數據分析提升良率。

整合前測試可確保最終封裝中僅使用功能正常的晶片與中介層,並透過高效的 KGD 與 KGI 流程降低缺陷率。針對 3D 堆疊式積體電路,則透過先進的 3D-DFT 測試存取架構進行全面的可靠性與性能測試。

關鍵在於,ATE 的數據分析透過提供趨勢與異常現象的洞察,協助製造商在製造過程中獲得更強大的掌控力。人工智慧進一步協助分析這些趨勢——優化測試參數,並進行即時、主動的調整,從而實現良率提升與成本降低。泰瑞達的Archimedes 分析解決方案提供的是 一個開放的開發環境,可在邊緣端實現即時分析,並具備 兼具靈活性,能提供開箱即用與客製化 解決方案,且易於部署。

同樣地,旨在降低資料中心功耗的矽光子學,也必須同步開發數位與光子學的測試技術。隨著光子學為實現高資料傳輸速率與低功耗而日益常規地與電子元件整合,測試解決方案必須針對共封裝光學元件進行優化。

運用數據與自動化技術打造新一代自動測試設備(ATE)

展望未來幾年,我們預期針對新型半導體材料(例如碳化矽(SiC)和氮化鎵(GaN))以及整合光子學的專用測試設備需求將大幅增加。這包括提升高電壓/高電流與低電壓/低電流測試的能力,並能有效處理單一封裝內的不同材料。

端到端自動化預計將發揮關鍵作用,透過從晶圓到最終封裝的完全自動化測試流程,減少人工干預並將錯誤降至最低。自動測試設備(ATE)將持續運用人工智慧與機器學習,以提升測試精準度、預測元件故障,並即時優化測試參數。

由人工智慧驅動的數據分析將有助於識別模式與趨勢,從而實現主動式品質管控並提升產量。泰瑞達正透過「SEMI 智慧數據與人工智慧倡議」支持業界導入人工智慧的舉措;該平台專為半導體生態系統設計,旨在推動數據與人工智慧創造價值。作為該倡議的成員,泰瑞達致力於標準化測試數據輸出格式,此舉有助於促進合作,同時無須擔心智慧財產權外洩或供應商鎖定問題。

顯而易見,人工智慧、先進半導體技術與地緣政治動態的交匯,正在塑造我們產業的未來。透過靈活、協作且創新的測試策略,泰瑞達致力於確保半導體的可靠性與卓越品質,為人工智慧充分發揮潛力的未來鋪平道路。

Jeorge S. Hurtarte 博士目前擔任泰瑞達(Teradyne)半導體測試部門的產品行銷資深總監。Jeorge 曾在泰瑞達、Lam Research、LitePoint、TranSwitch 及 Rockwell Semiconductors 擔任過各種技術、管理及高階主管職務。他是 IEEE 802.11 Wi-Fi 標準委員會的投票委員,並擔任 IEEE 802.11ay 工作組的秘書。 Jeorge 目前擔任 IEEE 異質整合路線圖 (HIR) 測試工作組的共同主席,並兼任加州大學聖克魯茲分校及鳳凰城大學的客座教授。