先進封裝與微晶片技術需要精密且靈活的測試策略

異質整合正推動半導體產業的創新,但同時也為晶片設計帶來更多複雜性,進而導致測試要求更加嚴苛。自動測試設備(ATE)產業正積極因應,開發並運用更先進的測試設備,以處理測試異質晶片所需的各種功能與介面。這包括對不同通訊協定、電源域及熱特性進行測試——最終針對每一組整合元件,皆採用其專屬的參數與性能標準。

異質整合概覽

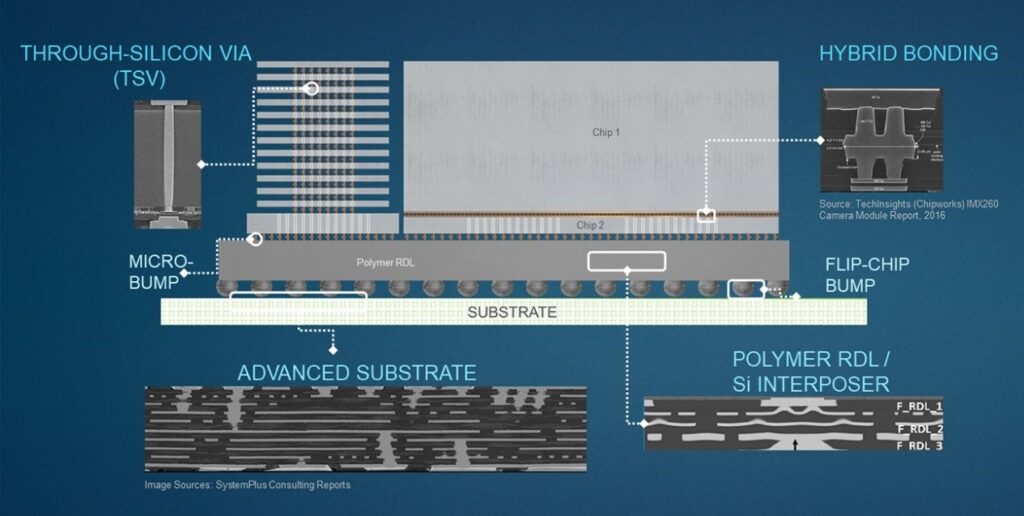

異質晶片(亦稱為異質整合)是指將多個獨立製造的元件(例如處理器、記憶體、感測器)整合至單一封裝或系統級封裝(SiP)中。以這種方式整合的元件稱為「小晶片」(chiplets),其製造可採用不同的製程與材料。圖 1 展示了一種異質整合的實例。

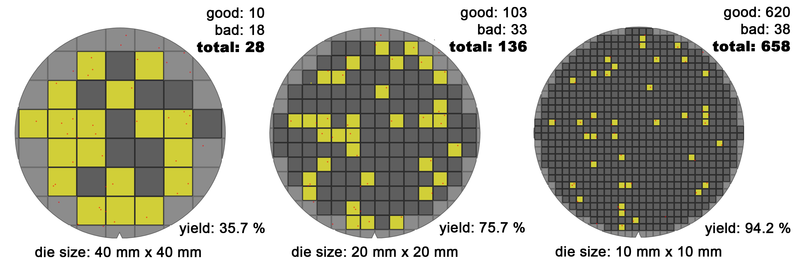

透過運用各種技術與材料,製造商所打造的 SiP 能夠比傳統的單一晶片更有效地執行多項運算任務。系統設計師得以在更小的佔用空間內,獲得更高的效能、更低的功耗以及更強大的功能。 與單晶片裝置相比,小晶片(chiplets)的微小尺寸有助於顯著提高良率,因此,在相同的裝置缺陷密度下,成本也隨之降低,如圖 2 所示。這些是推動人工智慧、5G 和物聯網等先進應用的關鍵因素,因為這些領域必須在嚴格的功耗與空間限制下,滿足多樣且密集的運算需求。

隨著技術的進步,幾乎任何裝置都能根據應用需求整合於異質封裝中。因此,測試資源必須能夠測試幾乎任何類型的功能,同時兼顧從低階到高階的各種經濟考量。

對測試產業的全面影響

由於複雜性增加——包括需要更先進的測試設備(例如泰瑞達的UltraFLEXplus)以及測試時間可能延長——因此優化品質成本至關重要。然而,由於不同元件之間可能產生的交互作用,確保異質晶片的可靠性更具挑戰性。

由於任何元件的缺陷都可能影響晶片的整體功能,產能管理也隨之變得更加複雜。靈活的測試解決方案可能包含專用的測試演算法和測試治具,以精確評估每顆獨特晶片的性能與可靠性。

靈活的測試策略是必不可少的

為因應先進數位晶片與異質整合的複雜性,目前已採用多種測試策略。動態測試覆蓋率架起了自動測試設備(ATE)與system level test (SLT)之間的橋樑,能在模擬終端使用環境的條件下評估半導體元件。泰瑞達(Teradyne)的TitanSLT 平台便是其中一例,在需要最高等級系統性能測試的半導體測試環境中,提供靈活性、可擴展性與高密度。 透過模擬真實世界情境,動態測試覆蓋率能有效識別那些在其他情況下可能隱藏的故障。此策略透過平衡測試成本與提升故障檢測能力,有助於優化品質成本。此外,它還讓製造商能運用數據分析來提升良率,確保只有最高品質的產品才能進入市場。

「左移」與「右移」策略能進一步平衡製造流程中的測試覆蓋率。「左移」將測試前移至開發流程的早期階段,透過更早發現並解決缺陷,從而降低整體成本。相反地,「右移」則將測試延伸至後期階段,包括製造完成後,確保任何潛在缺陷在產品送達消費者手中之前被發現。這兩種策略相輔相成,共同優化成本、品質與良率。

測試的複雜性帶來挑戰

在 2.5D/3D 封裝中測試已知良品晶片 (KGD) 和已知良品中介層 (KGI),會面臨許多必須考量的挑戰。 整合過程相當複雜,由於晶片與中介層在 3D 堆疊結構中形成多層互連,且具備多種功能。這些元件的微型化更增加了測試難度,原因在於透過矽貫通孔(TSV)等複雜連接結構,以及供測試探針使用的物理空間縮減。

晶粒內的缺陷可能要等到元件完成整合後才會顯現。堆疊與鍵合的製程本身,可能會因熱應力與機械應力而引入新的缺陷,或加劇現有的缺陷。一旦元件完成堆疊,要接觸各層進行測試便變得更加困難,需要採用先進的探測技術與測試存取機制。

高速互連技術(包括貫通式垂直孔結構)進一步增加了測試的複雜性。貫通式垂直孔(TSV)能穿透矽晶片提供垂直連接,對於高密度、高性能封裝至關重要。然而,其複雜的特性在訊號完整性、熱管理、製造變異性及測試可及性方面帶來重大挑戰,使得測試工作更加艱鉅。 必須調整「可測試性設計」(DFT)方法,以滿足 3D 封裝測試的特定需求,確保全面的故障覆蓋率並將漏測率降至最低。透過整合內建自測試(BIST)結構、擴展邊界掃描技術、實施熱感知測試、確保缺陷容忍度,以及採用分層測試方法,製造商能夠提升先進 3D 半導體封裝的可靠性與性能。

作為測試領域的領導者,泰瑞達(Teradyne)遵循IEEE 1838 標準來應對這些挑戰,並充分利用其在 3D 堆疊積體電路測試存取架構方面的全面框架。IEEE 1838 確立了標準化的測試介面與協定,確保來自不同製造商的各種元件都能透過共同的框架進行測試。 該標準支援模組化測試存取架構,可在不同層級與元件間實現可擴展且靈活的測試。根據 IEEE 1838 指南整合 BIST 電路與 DFT 功能,有助於實現更高的故障覆蓋率。為此,泰瑞達的UltraFLEX以及 UltraFLEXplus,以及其 ETS-88 測試機,皆能為更高複雜度的裝置提供測試能力,同時提升精準度並降低客戶的擁有成本。

展望未來的持續創新

在追求更高性能、更高整合度及更低功耗的需求驅動下,半導體產業正持續演進。在對半導體測試產生重大影響的新興技術中,包括「通用晶片互連快取」(UCIe)等產業互連標準,以及共封裝矽光子學技術的問世。

隨著 UCIe 和矽光子技術的應用,互連結構日益複雜,因此需要採用先進的測試方法來確保訊號完整性與效能。這包括對高速訊號進行精確的特性分析,以及對光子元件進行嚴格的測試。

共封裝解決方案必須採用有效的熱管理策略,以防止過熱並確保可靠運作。測試過程必須考量熱效應,並採用具備熱感知的測試技術。

隨著這些新興技術持續發展,半導體產業將受益於性能提升、整合能力增強以及功耗效率的改善。然而,測試的複雜性也將隨之增加,這要求測試方法與設備必須持續創新,以應對這些異質系統所帶來的獨特挑戰。透過領先這些趨勢,並採用標準化方法與靈活的測試策略,測試產業將有助於確保下一代半導體元件能夠可靠且高效地量產。

Jeorge S. Hurtarte 博士目前擔任泰瑞達(Teradyne)半導體測試部門的產品行銷資深總監。Jeorge 曾在泰瑞達、Lam Research、LitePoint、TranSwitch 及 Rockwell Semiconductors 擔任過各種技術、管理及高階主管職務。他是 IEEE 802.11 Wi-Fi 標準委員會的投票委員,並擔任 IEEE 802.11ay 工作組的秘書。 Jeorge 目前擔任 IEEE 異質整合路線圖 (HIR) 測試工作組的共同主席,並兼任加州大學聖克魯茲分校及鳳凰城大學的客座教授。