隨著半導體產業日益朝向微晶片、2.5D/3D封裝及異質整合發展,測試領域正面臨重大的新挑戰。像泰瑞達(Teradyne)這樣的業界領導者雖具備應對並推動創新的必要技術,但為了維持產業的順暢運作,我們需要有效的合作,而這正是標準化的關鍵所在。

在測試生態系統中,標準在多個領域都至關重要,旨在促進高效協作、鼓勵創新,並提升測試效率。從宏觀層面來看,這些標準皆與積體電路(IC)及半導體元件的測試與通訊協定相關,從而確保先進系統的互通性、資料傳輸及可靠性。

相關標準包括:

- PCIe(周邊元件互連快取):一種用於連接電腦元件的高速通訊標準

- MIPI(行動產業處理器介面):一種用於行動裝置的高速通訊標準

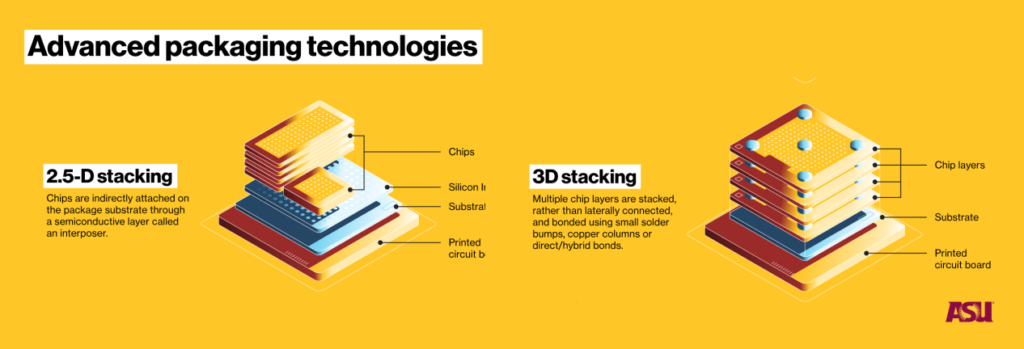

- UCIe(通用小晶片互連快車):專注於在異質系統中建立小晶片與 2.5D/3D 封裝之間的高效互連。

- IEEE 1838:制定了 3D 積體電路測試的標準,特別是針對具有貫穿矽通孔(TSV)的元件。

- JTAG1、1149.6 及其變體 J2C:用於測試與診斷積體電路內部互連的邊界掃描標準

- SPI(串列周邊介面):一種常用於連接微控制器與周邊裝置的通訊協定。

這些標準共同確保了半導體元件在高度互聯的生態系統中,能夠實現無縫的功能運作、可製造性及可擴展性。請繼續閱讀泰瑞達(Teradyne)的 Jeorge Hurtarte 的分析,他將探討這些關鍵標準、其對測試的影響,以及泰瑞達對統一測試生態系統的願景。

用於測試高效能晶片的標準介面

產業標準透過建立一致的方法來評估半導體元件的功能、性能及可靠性,在確保半導體測試的有效性方面發揮著關鍵作用。這些標準有助於應對日益複雜的半導體設計、先進封裝技術以及異質元件整合所帶來的挑戰。

首先,有標準介面可用於連接高性能運算晶片,例如 GPU 和 CPU——無論它們是採用傳統封裝還是基於小晶片(chiplet)的設計。這些介面通常為序列式,例如PCIe和 MIPI。

這些串列埠可用於透過掃描測試來檢測裝置的內部數位元件。在此,雖然使用的是串列介面,但已轉換為更接近並行處理的方式,透過連接晶片內建的「鏈路」來同時測試所有電晶體。掃描測試需要測試機具備大量的記憶體,而業界的普遍趨勢是記憶體容量不斷增加。

此外,掃描測試也有不同類型,其中部分由新思科技(Synopsys)或西門子(Siemens)等 EDA 公司主導。泰瑞達(Teradyne)會及早與這些公司合作,以了解其 EDA 工具在該類掃描測試方面能提供哪些功能——這有助於進行前瞻性規劃,並確保公司能在測試與工具整合方面佔據有利地位。

西門子等業界領導者正積極推動將監測器直接整合至晶片中。這些微型運算裝置能監控晶片內特定區塊的狀態,並提供關於運算效能、可靠性及潛在故障的健康狀態數據。標準化序列介面與晶片內監測器的結合,對於支援自動測試設備(ATE)應對現代晶片極度複雜的挑戰至關重要。

那麼,針對晶片模組的標準又是如何呢?

就新興的「晶片模組(chiplets)」技術而言,最廣為人知的標準或許是 UCIe,該標準專注於晶粒或晶片模組之間的互連。UCIe 針對晶片模組的傳輸距離僅有數毫米,這帶來了可測試性方面的問題。這可能意味著測試設備對靜電放電(ESD)的敏感度會提高,而這正是泰瑞達(Teradyne)有所貢獻的領域。

應採用IEEE 1838 標準(即 3D 堆疊積體電路測試存取架構標準),以執行封裝前與封裝後的測試。IEEE 1838 是一項針對 3D 積體電路的 DfT(可測試性設計)標準。DfT 闡述了如何建構一種架構,使其能夠分別測試多個可能包含嵌入式核心與 3D 互連結構的堆疊晶片。

中介層的測試主要可透過點對點導通測試來完成。已知良品中介層(KGI)對於確保先進封裝的足夠良率至關重要。

在封裝後組裝階段,IEEE P1838 的主 TAP 埠與次級 TAP 埠可讓測試人員驗證晶粒間測試存取通道及互連性能的完整性。

更多標準及其對測試的影響

新興標準包括 JTAG 1149.1 或 1149.6、SPI 以及 J2C(JTAG 至 CPU)。這些標準在設計與製造階段,對於確保積體電路(IC)的有效通訊、除錯及驗證,皆扮演著關鍵角色。

JTAG 1149.1(亦稱為 IEEE 1149.1 標準)用於邊界掃描測試。它允許在不需實體測試探針的情況下,對 PCB 上的個別元件進行測試。此標準提供了一種存取並測試 IC 內部訊號的方法,從而能夠偵測開路、短路及互連問題等故障。 JTAG 支援晶片與電路板在製造完成後的測試,對於除錯及驗證電路行為是否正確至關重要。

JTAG 1149.6 擴展了 1149.1 標準,以支援對現代積體電路中日益普遍的高速差分訊號(例如 LVDS、USB 及高速序列介面)進行測試。此標準可測試這些高速介面的完整性,確保其正常運作,特別是在傳統邊界掃描技術無法充分測試訊號品質與傳輸效能的系統中。

J2C 是 JTAG 的一種變體,用於直接連接至 CPU 或 SoC(系統單晶片)以進行測試、除錯及編程。J2C 能存取 CPU 的內部狀態、寄存器及記憶體,以供測試之用。這在半導體測試中至關重要,特別是在開發複雜處理器時的除錯,以及驗證 CPU 或 SoC 在製造完成後是否如預期般運作。

在半導體測試環境中,SPI 是一種常被用於與晶片或電路板上的嵌入式元件或記憶體裝置進行通訊的序列通訊協定。測試設備透過 SPI 與積體電路(IC)進行介接,以執行功能驗證、資料傳輸測試及記憶體編程。

這些標準在半導體測試中至關重要,因為它們為測試設備與被測裝置(DUT)之間提供了存取、控制及通訊路徑。這些標準能協助偵測故障,識別短路、開路或訊號完整性等問題。透過讀取與寫入測試圖案,它們確保裝置能正確運作,並透過協助工程師在設計與製造階段精準定位並解決問題,從而推動除錯與驗證工作。這些即時資料可與其他測試系統共享,以提升測試效率。

數據標準可提升效率

半導體測試會產生海量數據——若能即時將這些數據與數據分析平台及其他下游系統共享,將帶來巨大的效率與良率效益。

然而,不同公司的資料格式可能無法互通。SEMI 的「智慧資料與人工智慧倡議」透過提供一個框架,讓晶圓廠內各部門之間能夠共享資料,從而解決此問題。

「SEMI 的『智慧數據與人工智慧』計畫促進整個生態系統的協作,運用數據分析、機器學習、人工智慧及數位孿生技術於半導體製程中,」SEMI 智慧數據與人工智慧計畫全球負責人暨策略技術顧問 Pushkar Apte 博士表示。「隨著半導體元件及其用於測試性能、可靠性與整體品質的自動測試設備(ATE)系統日益複雜,這份共享的洞見對於加速創新步伐至關重要。」

作為此倡議的成員,泰瑞達正致力於標準化測試資料輸出格式,此舉將促進業界合作,同時避免智慧財產權外洩或供應商鎖定的風險。該公司已設計出「泰瑞達阿基米德(Teradyne Archimedes)」分析解決方案,這是一個開放式開發環境,旨在支援不依賴特定供應商的分析策略。

Archimedes 提供即時存取測試資料的功能,使分析更有效率,決策更迅速。透過支援標準化的資料架構,泰瑞達正致力於打造一個更具協作精神與創新力的半導體生態系統。

標準、協作與測試整合

在人工智慧、異質整合與微晶片(chiplets)的時代,一系列標準有助於確保複雜的半導體系統能夠獲得高效且精準的測試,從而讓高品質的產品得以推向市場。

隨著半導體產業持續演進,泰瑞達始終站在制定與實施標準的前沿,這些標準將塑造未來測試的樣貌。從 UCIe 和 IEEE 1838 等與小晶片相關的標準,到透過「智慧數據與人工智慧倡議」所推動的數據標準,泰瑞達的貢獻正為基於即時測試數據存取的半導體測試流程,鋪設出更高效、可靠且具協作性的道路。 展望未來,泰瑞達將持續在定義與推動下一代半導體技術所必需的標準方面,發揮關鍵作用。

Jeorge S. Hurtarte 博士目前擔任泰瑞達(Teradyne)半導體測試部門的產品行銷資深總監。Jeorge 曾在泰瑞達、Lam Research、LitePoint、TranSwitch 及 Rockwell Semiconductors 擔任過各種技術、管理及高階主管職務。他是 IEEE 802.11 Wi-Fi 標準委員會的投票委員,並擔任 IEEE 802.11ay 工作組的秘書。 Jeorge 目前擔任 IEEE 異質整合路線圖 (HIR) 測試工作組的共同主席,並兼任加州大學聖克魯茲分校及鳳凰城大學的客座教授。