隨著半導體系統日益複雜,對新裝置進行除錯已成為一項重大挑戰。工程師必須處理複雜的硬體與軟體交互作用,且往往難以釐清問題的根本原因。問題發現並解決得越早,裝置就能越快上市。然而,這個過程可能既耗時又耗費大量資源——特別是在處理尖端技術時更是如此。

恩智浦透過泰瑞達 Portbridge 與 Lauterbach TRACE32 加速產品上市時程

挑戰

現代嵌入式處理器仰賴複雜的開機韌體來初始化硬體,並為系統運作做好準備。然而,這套韌體在早期測試階段也可能帶來挑戰——特別是在出現問題時。在探針台進行首片晶片除錯時,恩智浦半導體(NXP® Semiconductors)——汽車、工業與物聯網、行動通訊及通訊基礎設施市場中創新解決方案的信賴夥伴——便遇到了這樣的挑戰。 由於難以掌握系統早期狀態的詳細資訊,加上晶圓探針測試的複雜性,調試開機韌體問題尤為困難。解決這些問題通常需要跨多個工程領域的協作。

泰瑞達的解決方案

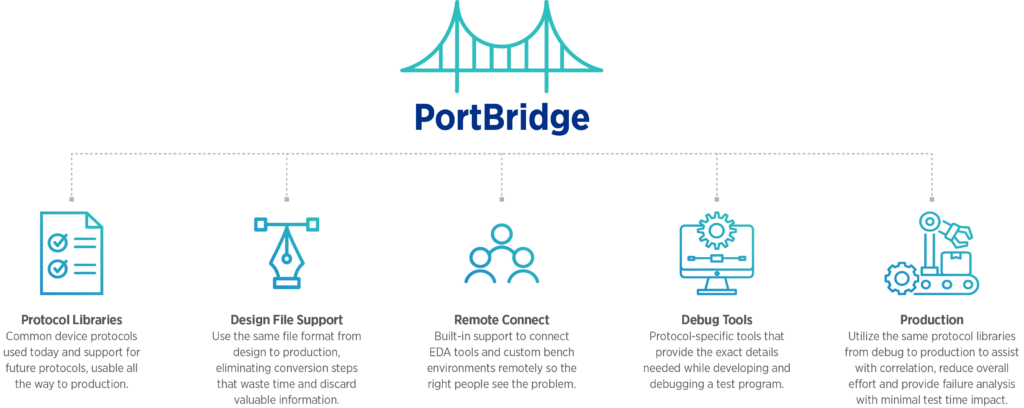

透過採用 TeradynePortBridge(該解決方案可簡化從測試設計到量產的流程),恩智浦得以直接在 UltraFLEXplus 測試機上直接進行核心除錯,並搭配Lauterbach 的TRACE32® 工具套件——這套由尖端硬體與軟體元件組成的解決方案,能協助工程師分析、優化及驗證各類嵌入式系統。

通常情況下,恩智浦(NXP)必須等到封裝好的元件到手後才能開始除錯。然而,透過將 PortBridge 與 Lauterbach 的 TRACE32 結合使用,他們主動彙整並分享了配置指示,協助全球驗證團隊避免了此問題。

解決方案的優勢

透過採用泰瑞達 (Teradyne) 的 PortBridge 以及 Lauterbach 的 TRACE32 工具,恩智浦 (NXP) 的除錯時間獲得了顯著縮短。該團隊得以在晶圓層級即開始診斷故障,比以往必須等待封裝元件的流程提早了兩週。在晶圓探針台上使用 PortBridge,使他們能夠迅速解決問題,並如期達成客戶的交貨里程碑。

此外,由於他們能在收到封裝零件之前,便向全球團隊分享詳細的操作指引,因此驗證流程得以簡化。最後,透過在測試台與UltraFLEXplus 之間靈活調度測試任務,NXP 團隊UltraFLEXplus 在開發週期的更早期階段獲取洞見並落實改進措施。

部署

隨著產品上市時程不斷縮短,工程資源也日益緊繃,Lauterbach 的 TRACE32 和 Teradyne 的 Portbridge 等工具,能協助企業在確保產品準時交付的同時,最大限度地提升工程產能。恩智浦(NXP)目前正積極探索 Portbridge 的更多應用場景,善用其在測試台與測試機之間傳輸腳本、記錄並轉錄交易資料,以及透過協定感知功能擷取裝置輸入與輸出資料(無需生成新測試模式)等能力。