人工智慧(AI)正在改變各行各業,提升我們的日常生活品質,並提高效率與決策能力 ,但其對運算處理能力的需求正以驚人的速度增長,每三個月便翻倍一次 (圖 1)。 為 維持 這股勢頭,半導體產業正突破傳統晶片開發的框架 ——已邁入異質整合的時代微晶片 微晶片 在先進 積體封裝中。

(圖 1: 成長 運算需求。 來源: https://openai.com/index/ai-and-compute/)

微晶片的崛起

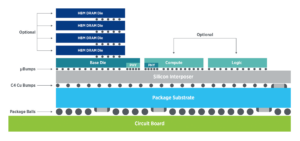

像NVIDIA和AMD這樣的晶片公司正在重寫遊戲規則,設計出將多個 CPU 和 GPU 整合於單一先進封裝中,並搭配高頻寬記憶體的架構 (HBM)。人工智慧工作負載需要快速存取海量資料,而整合 HBM 正是實現此目標的關鍵。這種將兩個、四個或更多處理核心與 HBM 堆疊結合的方法,需要採用台積電開發的一種複雜且先進的封裝技術,稱為 CoWos®(晶片上晶圓上基板), 通常稱為 2.5/3D 封裝 (圖 2)。 此類封裝尺寸可超過 100 mm × 100 公釐 ,並需要能夠處理大型晶圓中介層的探針機 CoW 模組/堆疊, 此外 滿足顯著更高的散熱需求,詳情如下所述。

(圖 2:2.5D/3D 封裝架構,來源:泰瑞達)

為了維持最佳效能,這些異質整合的先進封裝元件需要專屬的高速介面才能有效進行通訊。所有這些需求都使得半導體產業的格局日益複雜。

隨著晶片技術的進步,測試工作也變得更加複雜

隨著封裝複雜度的增加,對更周詳的測試策略的需求也隨之提升。 在從單一晶片過渡到小晶片(chiplets)的過程中,傳統的測試方法未必能直接沿用,因為測試 IP 現已分散於多個晶片之上,甚至在某些情況下,還橫跨不同的設計團隊或公司。這種分散化現象要求我們更明確地界定各階段(晶片、橋接器、中介層、基板及堆疊)必須測試的內容,以及適用於各範圍的標準或技術。

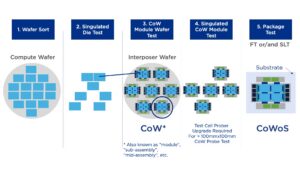

將多個晶粒封裝至單一基於小晶片的系統中,雖是一項重大進展,卻也帶來了一項關鍵挑戰:必須在最終組裝前驗證每個元件是否運作正常。多晶粒封裝需要經過嚴格的篩選以避免良率損失,僅對晶粒進行驗證是不夠的。中介層、基板、橋接器及堆疊結構也必須透過適用於各層的測試技術進行驗證。 因此,產業正邁向「全系統良品驗證」(known-good-everything),從「晶片良品驗證」(KGD)到「中介層良品驗證」(KGI),再到「CoW 良品驗證」(KG-CoW),以此類推。(圖 3)

(圖 3:為確保 KGD 和 KG-CoW 而可能進行的測試插入點。來源:Teradyne)

晶片間的高速通訊為系統增添了額外的複雜性。晶片必須以極高的速度交換資料——例如在 GPU 與 HBM 之間的資料傳輸過程中——然而各製造商的物理與電氣介面卻各不相同。儘管像通用晶片互連快車 (UCIe™) 這樣的開放標準持續演進,但晶片介面之間仍存在顯著差異。 為因應這種多樣性,測試解決方案日益需要具備裝置原生協定行為特性的介面 IP,以避免電氣過載或探針相關損壞。部分供應商現已提供符合 UCIe 標準的 PHY 和控制器 IP,供裝置製造商整合使用,使自動測試設備 (ATE) 平台能夠安全且一致地測試高速鏈路。

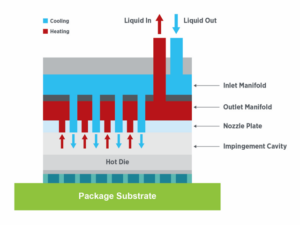

(圖 4:晶片級裸片散熱,來源:泰瑞達)

製造商和測試人員也必須密切關注熱管理。更強大的處理能力意味著更多的散熱問題,這需要採用先進的冷卻方法——甚至可能需要在封裝內部採用液冷技術 (圖 4)。 封裝內晶片數量增加意味著連接點增多,因此測試儀器需要投入更多資源。晶體管數量增加則意味著電源電流需求更高、需配置更多電源儀器,並帶來更嚴峻的熱管理挑戰,這需要創新的冷卻解決方案以及先進的自適應熱控制(ATC)策略。

最後,製造測試作業必須考量中介層(interposer)——這是一種物理介面層,用於將晶片與基板或其他有源元件進行電氣連接。例如,多層或 2.5D 封裝包含多個晶粒,這些晶粒安裝在基板頂部的中介層上。該中介層的功能如同一個微型矽板,負責將訊號從上層晶粒傳輸至下層晶粒。 為了確保先進封裝的良率達到要求,中介層本身必須是已知良品晶片(KGI)或已知良品中介層(KGI),這一點至關重要。

泰瑞達的解決方案

隨著每一代裝置的推出,半導體元件的數量不斷增加,導致測試複雜度隨之提升。測試複雜度的增加,促使對掃描模式記憶體的需求日益增長。為此,泰瑞達(Teradyne)已增設額外的掃描記憶體,以確保即使是最複雜的半導體設計也能獲得有效的測試。

泰瑞達 UltraFLEXplus 是一款自動測試設備 (ATE) 平台,可為計算裝置測試提供更快的吞吐量。 透過整合 Broadside 架構——該架構採用泰瑞達獨特的裝置介面板 (DIB) 設計UltraFLEXplus 更佳的訊號佈線,從而以較少的 DIB 電路板層數達到最佳訊號表現。Broadside 架構結合了兩大要素:首先是該公司的 PACE 架構,其特點是在測試機各處嵌入控制器以提升吞吐量;其次則是針對測試結果處理任務的分工機制。

鑒於將光學介面整合至這些先進裝置的趨勢,泰瑞達亦將先進的光學測試功能整合至其UltraFLEXplus 。這款業界首創的雙面晶圓探針解決方案,為新興的矽光子學及共封裝光學元件提供了高產能的測試方案,這些元件皆需同時進行電氣與光學測試。

此外,泰瑞達持續與領先的生態系供應商合作,以實現 該 對大型 異質整合 先進封裝 ,並符合最嚴格的先進自適應熱控測試要求 以實現從「已知良品晶片」到「已知良品CoW」乃至更遠的目標。

人工智慧與半導體測試的未來

業界日益認同,半導體測試是當今「小晶片」與先進封裝趨勢中不可或缺的一環。 隨著這股趨勢持續發展,人工智慧運算將以空前速度持續演進,並仰賴半導體測試發揮關鍵作用,確保高品質的裝置能在當今市場要求的縮短時程內順利上市。半導體測試將持續成為人工智慧驅動運算背後的無名英雄,穩步推動下一波技術突破的實現。

喬治·胡塔特博士目前擔任 測試部門 測試部門擔任資深總監暨首席行銷策略師。喬治曾在泰瑞達、Lam Research、LitePoint、 TranSwitch及 Rockwell Semiconductors 擔任過各類技術、管理及高階主管職務。Jeorge 現為 SEMI 北美諮詢委員會成員,並擔任 IEEE 異質整合路線圖 (HIR) 測試分會的共同主席。

Jeorge 擁有電機工程博士學位,以及三個碩士學位(工商管理、電腦科學與電信工程)。他同時也是 教授 。他同時擔任加州大學聖克魯茲分校及鳳凰城大學的客座教授。他是著作 《無晶圓廠積體電路技術解析》一書的合著者。