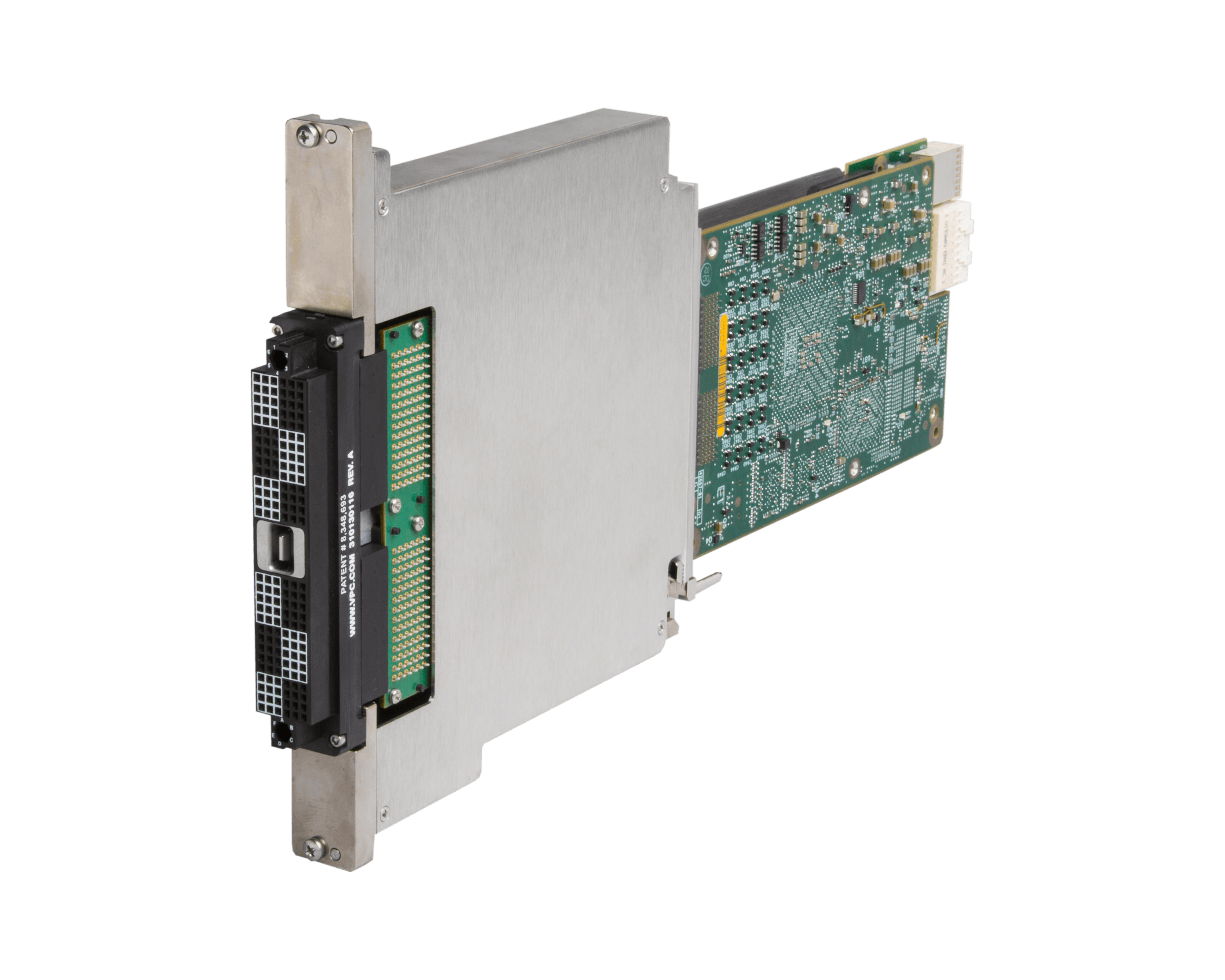

- 整合式儀表與維吉尼亞面板漏斗介面

- 配備 QuadraPaddle 介面模組的一體式儀器與漏斗組件

- 同時支援 i2 MX 纜線與 G20 ITA

- 3.3V LVTTL 支援 TTL 並與其相容

- 最多支援 64 個 LVTTL 輸入/輸出引腳,或 32 組 LVDS 差分對

- 廣泛支援 IEEE 1149.1 邊界掃描

- 支援各大第三方供應商的執行時軟體

- 透過大容量快閃記憶體編程進行的傳統互連測試

- 多個測試存取埠與高針腳數的平行 I/O

- 序列向量格式 (SVF) 執行時功能(TriFlex 軟體內含的HSSub )

- Teradyne eDigitalHSSub 提供傳統儲存模式(真值表)測試(此功能包含於HSSub 軟體中)

- 靈活的低階HSSub 1 I/O 匯流排處理

- 透過大型測試定義型 FPGA 和本地記憶體實現的HSSub 架構中,可重配置的HSSub (I/O 匯流排處理)

- 透過 Teradyne、終端使用者及第三方開發者所支援的HSSub ,可在數秒內完成設定

- 若需開發HSSub ,可透過基於標準設計模式的 FPGA 範本程式碼來簡化開發流程

- HSSub 基礎架構軟體介面可讓使用者透過 Windows Tier 3 或HSSub 2 儀器存取硬體