인공지능(AI)은 산업을 혁신하고, 우리의 일상을 풍요롭게 하며, 효율성과 의사결정 능력을 향상시키고 있습니다.을 향상시키고 있습니다 그러나 이에 필요한 연산 처리 능력은 놀라운 속도로 증가하고 있으며, 3개월마다 두 배로 늘어나고 있습니다 (그림 1). 이를 이 이 속도를 유지하기 위해, 반도체 업계는 기존의 칩 개발 방식을 넘어 – 이종 통합의 시대로 접어들었다칩릿 칩렛 고성능 집적 패키지의

(그림 1: 컴퓨팅 요구 사항의 컴퓨팅 요구 사항의 증가. 출처: https://openai.com/index/ai-and-compute/)

치플릿의 부상

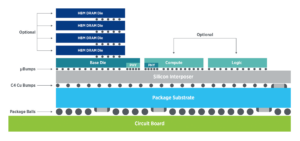

NVIDIA와 AMD 같은 반도체 기업들은 여러 개의 CPU와 GPU를 고대역폭 메모리(HBM)와 함께 단일 첨단 패키지에 통합하는 아키텍처를 설계하며 업계의 판도를 바꾸고 있습니다 (HBM)을 결합한 아키텍처를 설계하고 있습니다. AI 워크로드는 방대한 양의 데이터에 대한 신속한 접근을 필요로 하며, 이는 HBM 통합을 통해 가능해집니다. 두 개, 네 개 또는 그 이상의 처리 코어를 HBM 스택과 결합하는 이 접근 방식에는 TSMC가 개발한 CoWos®(Chip-on-Wafer-on-Substrate)라는 복잡하고 첨단 패키징 기술이 필요하며, 일반적으로 2.5/3D 패키징 (그림 2)라고 불립니다. 이러한 패키지는 100mm x 100mm 크기를 초과할 수 있으며, 대형 웨이퍼를 처리할 수 있는 인터포저 프로버가 필요합니다 CoW 모듈/스택을 처리할 수 있는 웨이퍼 인터포저 프로버가 필요합니다. 또한 아래에서 논의하듯이 훨씬 더 큰 열 방출 요구 사항도 충족합니다.

(그림 2: 2.5D/3D 패키징 아키텍처, 출처: Teradyne)

최상의 성능을 유지하기 위해서는, 이러한 이종 통합형 첨단 패키징 소자들이 효율적으로 통신할 수 있도록 독자적인 고속 인터페이스가 필요합니다. 이러한 모든 요인들이 반도체 산업의 복잡성을 점점 더 가중시키고 있습니다.

칩 기술의 발전에 발맞춰 테스트도 점점 더 복잡해지고 있다

패키지의 복잡성이 증가함에 따라, 보다 신중한 테스트 전략의 필요성도 커지고 있습니다. 모놀리식 다이에서 치플릿으로 전환되는 과정에서, 테스트 IP가 이제 여러 다이에 분산되어 있고 경우에 따라서는 서로 다른 설계 팀이나 회사에 걸쳐 있기 때문에, 오랫동안 확립되어 온 테스트 방법을 항상 그대로 적용할 수 있는 것은 아닙니다. 이러한 분산 구조로 인해 다이, 브리지, 인터포저, 기판, 스택 등 각 단계에서 무엇을 테스트해야 하는지, 그리고 각 범위에 어떤 표준이나 기법을 적용해야 하는지에 대한 명확한 정의가 필요합니다.

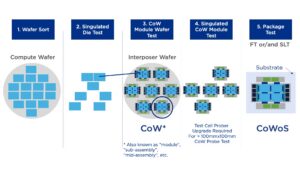

여러 개의 다이를 단일 칩렛 기반 시스템에 집적하는 것은 큰 진전이지만, 이는 최종 조립 전에 모든 구성 요소가 올바르게 작동하는지 검증해야 한다는 핵심적인 과제를 제기합니다. 다중 다이 패키지는 수율 저하를 방지하기 위해 엄격한 선별 과정이 필요하며, 다이만 검증하는 것만으로는 충분하지 않습니다. 인터포저, 기판, 브리지, 스택 역시 각 층에 적합한 테스트 기법을 사용하여 검증되어야 합니다. 따라서 업계는 'KGD(Known-Good-Die, 정상 다이)'에서 'KGI(Known-Good-Interposer, 정상 인터포저)', 'KG-CoW(Known-Good-CoW, 정상 CoW)' 등으로 이어지는 'Known-Good-Everything(모든 구성 요소 정상)' 방식으로 전환하고 있습니다. (그림 3)

(그림 3: KGD 및 KG-CoW를 보장하기 위한 가능한 테스트 삽입 위치. 출처: Teradyne)

치플릿 간의 고속 통신은 복잡성을 한층 더 가중시킵니다. 다이(die)들은 GPU와 HBM 간 데이터 전송과 같이 극한의 속도로 데이터를 교환해야 하지만, 제조사마다 물리적 및 전기적 인터페이스가 서로 다릅니다. UCIe™(Universal Chiplet Interconnect Express)와 같은 개방형 표준은 지속적으로 발전하고 있지만, 치플릿 인터페이스는 여전히 큰 차이를 보입니다. 이러한 다양성을 지원하기 위해, 테스트 솔루션은 전기적 과부하나 프로브 관련 손상을 방지하기 위해 장치의 네이티브 프로토콜과 동일하게 동작하는 인터페이스 IP를 점점 더 필요로 하고 있습니다. 일부 공급업체는 이제 장치 제조사가 통합할 수 있는 UCIe 호환 PHY 및 컨트롤러 IP를 제공하여, 자동화 테스트 장비(ATE) 플랫폼이 고속 링크를 안전하고 일관되게 테스트할 수 있도록 하고 있습니다.

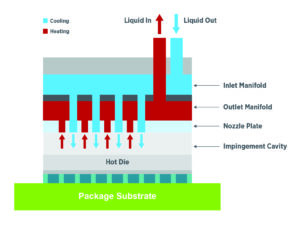

(그림 4: 칩 레벨 베어 쿨링, 출처: Teradyne)

제조사와 테스트 운영사는 열 관리에도 각별한 주의를 기울여야 합니다. 처리 능력이 높아질수록 발열 문제도 커지므로, 첨단 냉각 방식이 필요하며, 경우에 따라서는 패키지 내부에 액체 냉각 시스템을 적용해야 할 수도 있습니다 (그림 4). 패키지 내 다이 수가 늘어나면 연결점도 증가하므로 테스터에 더 많은 리소스가 필요합니다. 트랜지스터 수가 늘어나면 전원 공급 전류 요구량이 증가하고, 더 많은 전원 공급 장비가 필요하며, 혁신적인 냉각 솔루션과 첨단 적응형 열 제어(ATC) 전략을 요구하는 열 관련 과제도 더욱 커집니다.

마지막으로, 제조 테스트 공정에서는 칩을 기판이나 다른 능동 소자와 전기적으로 연결하는 물리적 인터페이스 층인 인터포저를 고려해야 합니다. 예를 들어, 다층 또는 2.5D 패키지는 기판 위에 조립된 인터포저에 여러 개의 다이가 탑재된 형태입니다. 이 인터포저는 소형 실리콘 기판의 역할을 하여 상단 층의 다이에서 하단 층의 다이로 신호를 전달합니다. 고성능 패키지의 충분한 수율을 보장하기 위해서는 인터포저 역시 '정상 작동이 확인된 다이(KGI)'여야 합니다.

테라다인의 솔루션

기기 세대가 바뀔 때마다 반도체 구성 요소가 늘어남에 따라 테스트의 복잡성도 높아지고 있습니다. 이러한 테스트 복잡성의 증가는 점점 더 많은 스캔 메모리 대한 수요를 불러일으키고 있습니다. 이에 대응하기 위해 테라다인(Teradyne)은 추가적인 메모리 탑재하여 메모리 아무리 복잡한 반도체 설계라도 효과적으로 테스트할 수 메모리 했습니다.

테라다인 UltraFLEXplus 는 컴퓨팅 장치 테스트에 더 빠른 처리량을 제공하는 ATE 플랫폼입니다. UltraFLEXplus 테라다인만의 독창적인 디바이스 인터페이스 보드(DIB) 설계 방식을 특징으로 하는 Broadside 아키텍처를 도입함으로써, 더 나은 신호 배선을 UltraFLEXplus DIB PCB 레이어 수를 줄이면서도 최상의 신호 성능을 구현합니다. Broadside는 두 가지 요소의 결합으로 이루어집니다. 첫째는 더 빠른 처리량을 위해 테스터 전반에 임베디드 컨트롤러를 탑재한 테라다인의 PACE 아키텍처이며, 둘째는 테스트 결과 처리를 위한 작업 분담입니다.

이러한 첨단 장치에 광학 인터페이스를 통합하는 추세를 반영하여, 테라다인(Teradyne)은 자사의UltraFLEXplus 첨단 광학 테스트 기능을 탑재하고 있습니다. 시장에 최초로 출시된 이 양면 웨이퍼 프로브 솔루션은 전기적 테스트와 광학 테스트가 모두 필요한 신흥 실리콘 포토닉스 및 코패키지드 옵틱스(CPO) 분야를 위한 대량 테스트 솔루션을 제공합니다.

또한, 테라다인은 선도적인 생태계 공급업체들과 지속적으로 협력하여 대형 대규모 이종 통합 첨단패키지의 가장 엄격한 첨단 적응형 열 제어 테스트 요건을 적용하여 “정상 칩(known-good-die)”에서 “정상 패키지(known-good-package)”로CoW” 및 그 이상의 목표를 향해.

AI와 반도체 테스트의 미래

반도체 테스트가 오늘날의 치플릿(chiplet) 및 첨단 패키징 트렌드의 필수적인 부분이라는 인식이 업계 내에서 점차 확산되고 있습니다. 이러한 흐름이 전개됨에 따라, AI 컴퓨팅은 전례 없는 진화 속도를 이어갈 것이며, 오늘날 시장이 요구하는 단축된 일정에 맞춰 고품질 장치가 시장에 출시될 수 있도록 반도체 테스트가 핵심적인 역할을 수행할 것이다. 반도체 테스트는 AI 기반 컴퓨팅의 숨은 주역으로서, 차세대 기술 혁신을 꾸준히 뒷받침할 것이다.

조르주 우르타르테 박사는 현재 컴퓨트 테라다인(Teradyne)의 컴퓨트 테스트 사업부에서 수석 이사 겸 수석 마케팅 전략가로 재직 중입니다. 조르주는 테라다인, 램 리서치(Lam Research), 라이트포인트(LitePoint), 트랜스위치, 록웰 세미컨덕터스 등에서 다양한 기술, 관리 및 임원직을 역임했습니다. 조르주는 SEMI 북미 지부의 자문위원으로 활동 중이며, IEEE 이종 통합 로드맵(HIR) 테스트 분과 위원회의 공동 의장을 맡고 있습니다.

Jeorge는 전기공학 박사 학위와 MBA, 컴퓨터 과학, 통신공학 석사 학위 등 총 세 개의 석사 학위를 보유하고 있습니다. 또한 그는 캘리포니아 대학교 산타크루즈 캠퍼스와 피닉스 대학교에서 입니다. 그는 캘리포니아 대학교 산타크루즈 캠퍼스와 피닉스 대학교의 객원 교수이기도 합니다. 그는 《팹리스 IC 기술 이해》의 공동 저자이기도 하다.