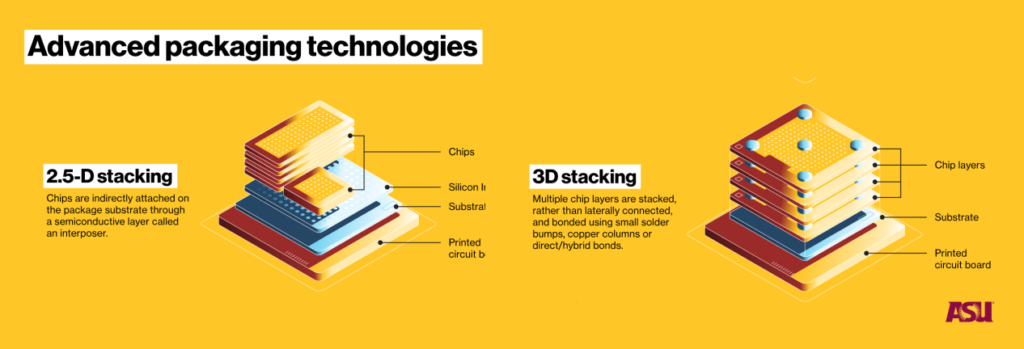

반도체 산업이 칩렛(chiplets), 2.5D/3D 패키징, 이종 통합(heterogeneous integration)으로 점점 더 전환됨에 따라, 테스트 분야에는 중대한 새로운 과제가 대두되고 있습니다. 테라다인(Teradyne)과 같은 선도 기업들은 이에 대응하고 혁신을 이끌어낼 수 있는 기술을 보유하고 있지만, 산업이 원활하게 운영되기 위해서는 효과적인 협력이 필요하며, 이를 위해서는 표준화가 필수적입니다.

테스트 생태계 내에서 효율적인 협력을 도모하고, 혁신을 촉진하며, 테스트 효율을 높이기 위해 표준이 중요한 역할을 하는 분야는 다양합니다. 큰 틀에서 볼 때, 이러한 표준들은 모두 집적회로(IC) 및 반도체 소자의 테스트 및 통신 프로토콜과 관련되어 있으며, 이를 통해 첨단 시스템에서 상호 운용성, 데이터 전송 및 신뢰성을 보장합니다.

관련 표준은 다음과 같습니다:

- PCIe(Peripheral Component Interconnect Express): 컴퓨터 구성 요소를 연결하는 고속 통신 표준

- MIPI(Mobile Industry Processor Interface): 모바일 기기에서 사용되는 고속 통신 표준

- UCIe(Universal Chiplet Interconnect Express): 이종 시스템 내에서 치플릿과 2.5D/3D 패키지 간에 효율적인 상호 연결을 구축하는 데 중점을 둡니다.

- IEEE 1838: 3D IC 테스트, 특히 실리콘 관통 전극(TSV)이 적용된 소자에 대한 표준을 규정합니다.

- JTAG1, 1149.6 및 그 변형인 J2C: IC 내부의 상호 연결을 테스트하고 진단하기 위한 바운더리 스캔 표준

- SPI(직렬 주변기기 인터페이스): 마이크로컨트롤러와 주변기기를 연결하는 데 사용되는 일반적인 통신 프로토콜입니다.

이러한 표준들은 종합적으로, 고도로 상호 연결된 생태계 내에서 반도체 소자의 원활한 기능성, 제조 가능성 및 확장성을 보장합니다. 테라다인(Teradyne)의 조르주 우르타르테(Jeorge Hurtarte)가 주요 표준과 테스트에 미치는 영향, 그리고 통합 테스트 생태계에 대한 테라다인의 비전을 심도 있게 분석한 내용을 계속 읽어보시기 바랍니다.

고성능 칩을 테스트하기 위한 표준 인터페이스

산업 표준은 반도체 소자의 기능, 성능 및 신뢰성을 평가하기 위한 일관된 방법을 확립함으로써 효과적인 반도체 테스트를 보장하는 데 결정적인 역할을 합니다. 이러한 표준은 점점 더 복잡해지는 반도체 설계, 첨단 패키징 기술, 그리고 이종 부품의 통합으로 인해 발생하는 과제들을 해결하는 데 도움을 줍니다.

먼저, GPU나 CPU와 같은 고성능 컴퓨팅 칩에 연결하기 위한 표준 인터페이스가 있습니다. 이는 칩이 기존 방식의 패키지로 제작되었든 치플릿 기반이든 상관없이 적용됩니다. 이러한 인터페이스는 일반적으로 PCIe나 MIPI와 같은 직렬 방식입니다.

이 시리얼 포트는 스캔 테스트를 통해 장치의 내부 디지털 회로를 테스트하는 데 사용할 수 있습니다. 이 경우 시리얼 인터페이스를 사용하지만, 이를 병렬 방식에 가깝게 변환하여 칩 내부에 내장된 “체인”에 연결함으로써 모든 트랜지스터를 동시에 테스트합니다. 스캔 메모리 대용량 메모리 필요하며, 업계 전반의 추세는 메모리 지속적으로 메모리 방향으로 나아가고 있습니다.

또한 다양한 유형의 스캔 테스트가 존재하며, 그중 일부는 시노프시스(Synopsys)나 지멘스(Siemens)와 같은 EDA 기업들이 주도하고 있습니다. 테라다인(Teradyne)은 이러한 기업들과 초기 단계부터 협력하여 해당 EDA 도구가 이러한 유형의 스캔 테스트에 어떤 기능을 제공하는지 파악함으로써, 사전 계획을 수립하고 테스트 및 도구 통합에 있어 유리한 입지를 확보하고 있습니다.

지멘스(Siemens)와 같은 선도 기업들은 칩에 모니터를 직접 탑재하는 방식을 적극 추진하고 있습니다. 이는 칩 내부의 특정 블록 상태를 모니터링하고, 연산 성능, 신뢰성, 잠재적 결함 등에 관한 상태 데이터를 제공하는 초소형 컴퓨팅 장치입니다. 표준화된 직렬 인터페이스와 온칩 모니터의 결합은 현대 칩의 엄청난 복잡성을 처리해야 하는 ATE(자동 테스트 장비)의 역할을 뒷받침하는 데 있어 매우 중요합니다.

치플릿에 특화된 표준은 어떤가요?

신흥 기술인 칩렛(chiplets) 분야에서 가장 잘 알려진 표준은 아마도 다이(die)나 칩렛 간의 상호 연결에 중점을 둔 UCIe일 것입니다. UCIe는 칩렛 간 통신 거리가 밀리미터 단위로 짧아 테스트 가능성에 대한 문제를 야기합니다. 이는 장비가 정전기 방전(ESD)에 더 민감해질 수 있음을 의미하며, 이는 테라다인(Teradyne)이 기여해 온 분야입니다.

3D 적층 집적회로용 테스트 액세스 아키텍처 표준인 IEEE 1838을 활용하여 패키징 전후 테스트를 수행해야 합니다. IEEE 1838은 3D IC를 위한 DfT(테스트를 고려한 설계) 표준입니다. DfT는 임베디드 코어와 3D 상호 연결 구조를 포함할 수 있는 여러 적층 다이를 개별적으로 테스트할 수 있는 아키텍처를 구축하는 방법을 규정합니다.

인터포저 테스트는 주로 점대점 연속성 검사를 통해 수행할 수 있습니다. 정상 작동이 확인된 인터포저(KGI)는 첨단 패키지의 적절한 수율을 보장하는 데 필수적입니다.

패키지 조립 후 단계에서, IEEE P1838의 1차 및 2차 TAP 포트를 통해 다이 간 테스트 액세스 및 상호 연결 성능의 무결성을 검증할 수 있습니다.

추가 표준 및 시험에 미치는 영향

새로운 표준으로는 JTAG 1149.1 또는 1149.6, SPI, J2C(JTAG to CPU) 등이 있습니다. 이들 각각은 설계 및 제조 단계에서 집적회로(IC)의 효과적인 통신, 디버깅 및 검증을 보장하는 데 중요한 역할을 합니다.

JTAG 1149.1(IEEE 표준 1149.1이라고도 함)은 바운더리 스캔 테스트에 사용됩니다. 이 표준을 사용하면 물리적 테스트 프로브 없이도 PCB상의 개별 소자를 테스트할 수 있습니다. 또한 이 표준은 IC의 내부 신호에 접근하여 테스트할 수 있는 방법을 제공함으로써, 개방 회로, 단락, 배선 문제 등의 결함을 감지할 수 있게 해줍니다. JTAG은 제조 후 칩과 보드를 테스트할 수 있게 해주며, 디버깅 및 올바른 회로 동작을 검증하는 데 필수적입니다.

JTAG 1149.6은 1149.1 표준을 확장하여, 최신 IC에서 점점 더 널리 사용되고 있는 고속 차동 신호(LVDS, USB, 고속 직렬 인터페이스 등)의 테스트를 지원합니다. 이 표준을 통해 이러한 고속 인터페이스의 무결성을 테스트하여 정상적인 작동을 보장할 수 있으며, 특히 기존의 경계 스캔(boundary-scan) 기술로는 신호 품질과 전송 상태를 충분히 테스트할 수 없는 시스템에서 그 효과가 두드러집니다.

J2C는 테스트, 디버깅 및 프로그래밍을 위해 CPU나 SoC(시스템 온 칩)에 직접 연결하는 데 사용되는 JTAG의 변형 방식입니다. J2C는 테스트 메모리 CPU의 내부 상태, 레지스터 메모리 대한 접근을 제공합니다. 이는 반도체 테스트에서 매우 중요한 역할을 하며, 특히 복잡한 프로세서 개발 과정에서의 디버깅과, 제조 후 CPU나 SoC가 예상대로 동작하는지 검증하는 데 필수적입니다.

반도체 테스트 환경에서 SPI는 칩이나 보드상의 내장형 메모리 통신하는 데 자주 사용되는 직렬 통신 프로토콜입니다. 테스트 장비는 SPI를 통해 IC와 연결되어 기능 검증, 데이터 전송 테스트 메모리 수행합니다.

이러한 표준은 테스트 장비와 피시험 장치(DUT) 간의 접근, 제어 및 통신 경로를 제공하므로 반도체 테스트에 필수적입니다. 이를 통해 단락, 개방 회로 또는 신호 무결성 문제와 같은 결함을 감지하고 식별할 수 있습니다. 또한 테스트 패턴을 읽고 쓰면서 장치가 올바르게 작동하도록 보장하며, 엔지니어들이 설계 및 제조 단계에서 문제를 정확히 찾아내고 해결할 수 있도록 지원함으로써 디버깅과 검증 작업을 뒷받침합니다. 이러한 실시간 데이터는 다른 테스트 시스템과 공유되어 테스트 효율성을 높일 수 있습니다.

데이터 표준은 효율성을 높여줍니다

반도체 테스트 과정에서는 방대한 양의 데이터가 생성되는데, 이를 데이터 분석 플랫폼 및 기타 하류 시스템과 실시간으로 공유하면 효율성과 수율 측면에서 막대한 이점을 얻을 수 있습니다.

그러나 기업마다 데이터 형식이 서로 호환되지 않을 수 있습니다. SEMI의 ‘스마트 데이터 및 AI 이니셔티브’는 팹 내의 다양한 부서 간에 데이터를 공유할 수 있는 프레임워크를 제공함으로써 이러한 문제를 해결합니다.

SEMI의 스마트 데이터·AI 이니셔티브 글로벌 책임자이자 전략 기술 고문인 푸쉬카르 아프테(Pushkar Apte) 박사는 “SEMI의 스마트 데이터·AI 이니셔티브는 반도체 공정에서 데이터 분석, 머신러닝, AI 및 디지털 트윈 기술을 활용하여 전체 생태계에 걸친 협력을 가능하게 합니다”라고 말했다. “반도체 소자와 그 성능, 신뢰성, 전반적인 품질을 테스트하는 ATE 시스템이 점점 더 복잡해짐에 따라, 이러한 공유된 통찰력은 혁신의 속도를 가속화하는 데 있어 매우 중요합니다.”

테라다인은 이 이니셔티브의 일원으로서 테스트 데이터 출력의 표준화를 추진하고 있으며, 이를 통해 지적 재산권 유출이나 벤더 종속의 위험 없이 협업을 촉진할 수 있을 것으로 기대하고 있습니다. 또한 테라다인은 벤더에 구애받지 않는 분석 전략을 지원하기 위한 개방형 개발 환경인 ‘테라다인 아르키메데스 (Teradyne Archimedes )’ 분석 솔루션을 개발했습니다.

아르키메데스는 테스트 데이터에 대한 실시간 접근을 제공하여, 보다 효율적인 분석과 신속한 의사결정을 가능하게 합니다. 테라다인은 표준화된 데이터 프레임워크를 지원함으로써, 더욱 협력적이고 혁신적인 반도체 생태계 조성을 돕고 있습니다.

표준, 협업 및 시험 통합

AI, 이종 통합, 칩렛이 주류를 이루는 오늘날, 다양한 표준들이 복잡한 반도체 시스템을 효율적이고 정확하게 테스트할 수 있도록 지원함으로써, 고품질의 제품이 시장에 출시될 수 있도록 돕고 있습니다.

반도체 산업이 지속적으로 발전함에 따라, 테라다인은 테스트의 미래를 주도할 표준을 개발하고 도입하는 데 있어 여전히 선두에 서 있습니다. UCIe 및 IEEE 1838과 같은 치플릿(chiplet) 관련 표준부터 ‘스마트 데이터 및 AI 이니셔티브(Smart Data & AI Initiative)’를 통한 데이터 표준에 이르기까지, 테라다인의 기여는 실시간 테스트 데이터 접근을 기반으로 한 보다 효율적이고 신뢰할 수 있으며 협업적인 반도체 테스트 프로세스의 길을 열어가고 있습니다. 앞으로도 테라다인은 차세대 반도체 기술에 필수적인 표준을 정의하고 주도하는 데 있어 핵심적인 역할을 계속해 나갈 것입니다.

Jeorge S. Hurtarte 박사는 현재 테라다인(Teradyne)의 반도체 테스트 그룹에서 제품 마케팅 수석 이사로 재직 중입니다. Jeorge는 테라다인, 램 리서치(Lam Research), 라이트포인트(LitePoint), 트랜스위치(TranSwitch), 록웰 반도체(Rockwell Semiconductors)에서 다양한 기술, 관리 및 임원직을 역임했습니다. 그는 IEEE 802.11 Wi-Fi 표준 위원회의 의결권 위원이며, IEEE 802.11ay 태스크 그룹의 서기를 맡고 있습니다. 조지는 현재 IEEE 이종 통합 로드맵(HIR) 테스트 워킹 그룹의 공동 의장을 맡고 있으며, 캘리포니아 대학교 산타크루즈 캠퍼스와 피닉스 대학교의 객원 교수로도 활동하고 있습니다.