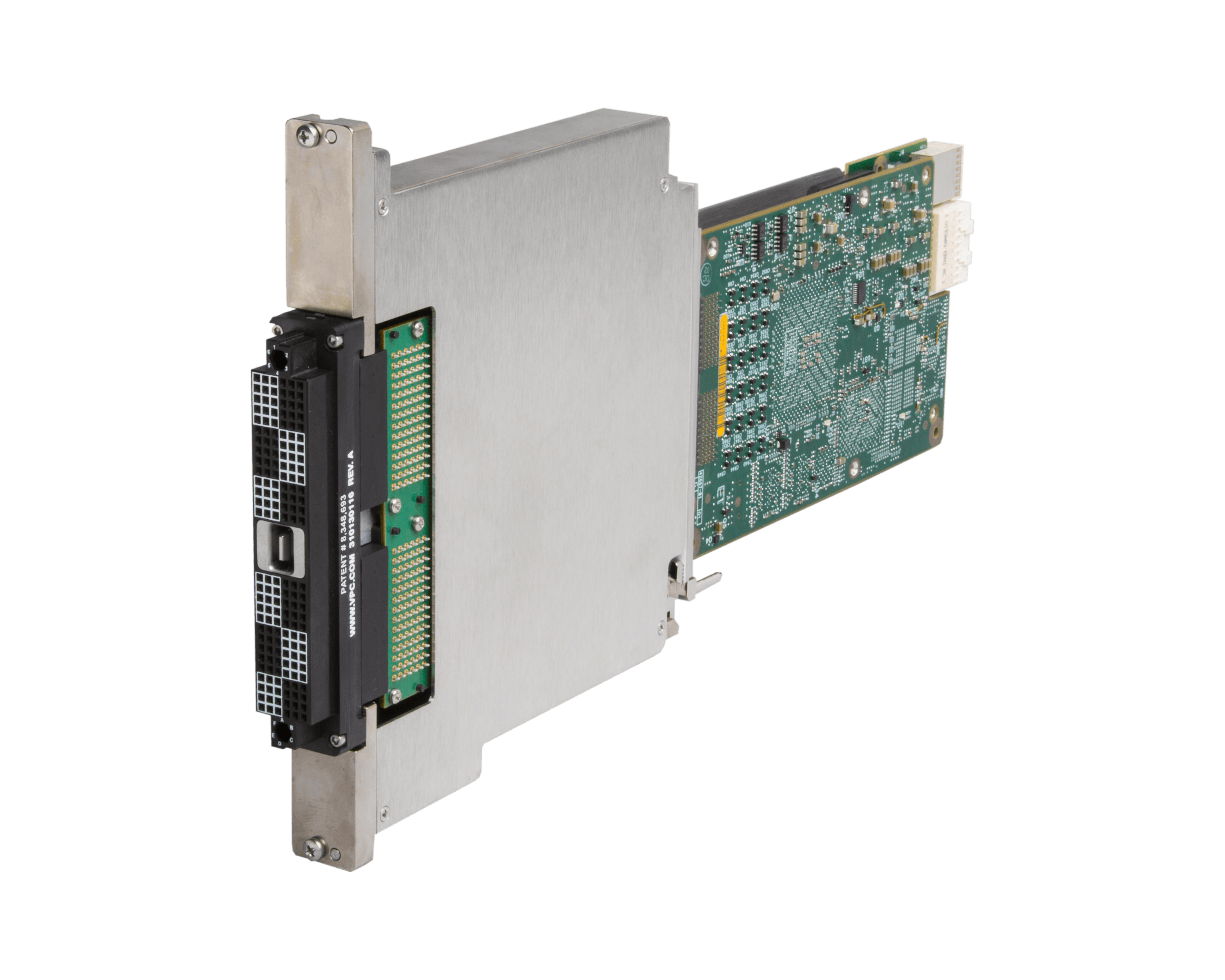

- 통합 계기 및 버지니아 패널 깔때기 인터페이스

- QuadraPaddle 인터페이스 모듈이 장착된 일체형 계기 및 깔때기 어셈블리

- i2 MX 케이블과 G20 ITA 모두 지원합니다

- 3.3V LVTTL은 TTL 호환이 가능하며 TTL과 호환됩니다

- 최대 64개의 LVTTL I/O 핀 또는 32개의 LVDS 차동 쌍을 지원합니다

- 광범위한 IEEE 1149.1 바운더리 스캔 지원

- 주요 타사 공급업체의 런타임 소프트웨어가 지원됩니다

- 대용량 플래시 프로그래밍을 통한 기존 상호 연결 테스트

- 다중 테스트 접속 포트 및 핀 수가 많은 병렬 I/O

- SVF(Serial Vector Format) 런타임 기능 (TriFlex 소프트웨어에 포함된HSSub )

- Teradyne eDigital HSSub 기존의 저장된 패턴(진리표) 테스트 기능을 제공합니다( HSSub 소프트웨어에 포함됨).

- 유연한 저수준 HSSub 1 I/O 버스 처리

- 대용량 테스트 정의 FPGA 및 로컬 메모리 통해 구현된HSSub 아키텍처의재구성 가능한 HSSub 1 (I/O 버스 처리)

- 테라다인(Teradyne), 최종 사용자 및 타사 개발자가 지원하는HSSub 통해 몇 초 만에 설정 가능

- 필요한 경우, 표준 설계 패턴을 기반으로 한 FPGA 템플릿 코드를 통해 HSSub 개발을 간소화할 수 있습니다.

- HSSub 인프라 소프트웨어인터페이스를 통해 Windows Tier 3 또는 HSSub 2 계측기에서 하드웨어에 액세스할 수 있습니다.