法規制、技術開発、そして人材環境の変化が影響を及ぼす状況において、テストリーダーは極めて重要な役割を担っています

半導体業界は急速に変化しており、生産能力の国内回帰に対する政府の支援により、アジア、米国、欧州の資源間の新たな相互作用が生まれている。一方で、業界はHBMやヘテロジニアス統合といった新技術の開発と維持にも取り組んでいる。 「CHIPS法(米国の半導体生産を促進するための有益なインセンティブ創出法)」や熟練エンジニアの不足、AI関連の新たな性能要件といった地政学的要因が、業界の課題と急速な進化に拍車をかけている。

これは半導体テストにとってどのような意味を持つのでしょうか。自動試験装置(ATE)メーカーは、技術の適応、自動化の推進、そして半導体メーカーとの緊密な連携を通じて、こうした課題の解決に重要な役割を果たしています。テストリソースは、業界がイノベーションを継続し、世界市場の拡大する需要に応え続けるために不可欠であることが明らかになっています。

地政学と半導体への影響

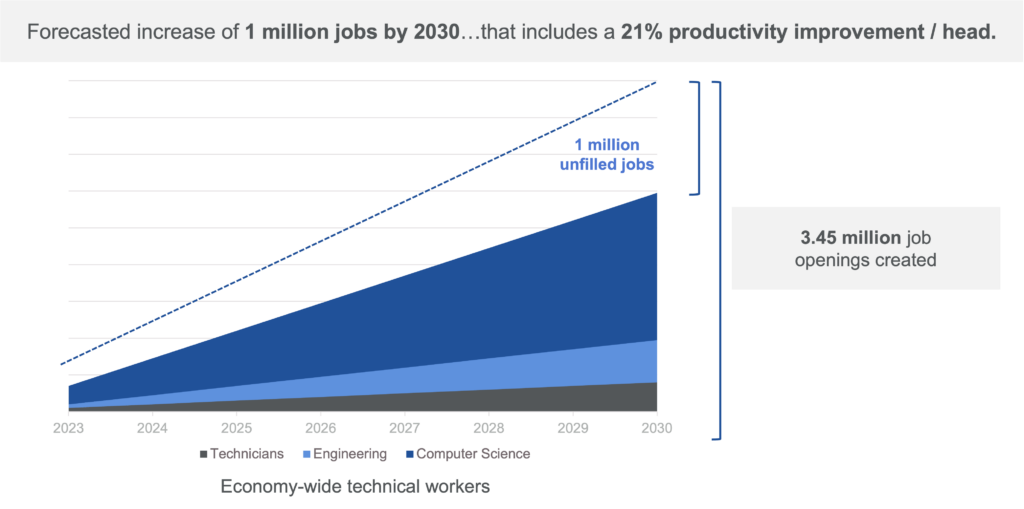

半導体市場は変化しており、製造能力の米国および欧州への回帰に対し、政府による支援が行われています。米国の「CHIPS法」は、国内の半導体製造および研究を強化するための重要な立法措置です。同法による多額の資金提供と優遇措置は、サプライチェーンの混乱や地政学的緊張によって露呈した脆弱性に対処することを目的としています。 また、この資金は人材育成にも充てられる。米国では今後数年間で7万~9万人の人材不足が見込まれており、生産性の向上にもかかわらず、2030年までに世界全体で100万人以上の求人が埋まらないと予測されている。

CHIPS法は、半導体技術の先端研究にも資金を提供しており、これにより半導体テスト手法や最先端のテスト装置におけるイノベーションの必要性が高まっています。高度なパッケージングやヘテロジニアス統合を特徴とするチップの複雑さに対応するためにテスト分野が進化していく中で、これは極めて重要であり、AIや高性能処理に対する幅広い需要に対応できるよう、業界が万全の態勢を整える一助となります。

欧州やアジアでも同様の取り組みが進められており、各地域がインフラの強化に努めている。地域間の相互関係は複雑だ。米国や欧州が自国の半導体エコシステムに巨額の投資を行っている一方で、アジア、特に台湾と韓国は依然として半導体製造の主要拠点であり続けている。

「CHIPS法」はテスト業界に多大な影響を与えています。資本の流入により半導体生産能力が拡大しており、その結果、より多くのテスト装置やサービスが必要とされています。米国国内に新たなファブや組立工場が設立されるにつれ、国内の半導体テストリソースに対する需要が高まっています。

テスト分野における新たな要求と新たな機会

こうした政府主導のインフラ投資は、半導体の設計、開発、およびテストにおいて極めて重要な局面で行われています。AIへの取り組みが進むにつれ、高度なデジタルチップの性能と信頼性への注目が高まっています。超高速な性能を必要とする一方で、複雑さと消費電力の増加を伴うアプリケーションに対する世界的な需要が高まっているのです。

半導体の微細化が進むにつれ(例えば5nm以下のプロセス)、その性能、信頼性、および電力効率を確保するための複雑さは飛躍的に増大しています。微細化が1段階進むごとに、製造精度、熱管理、欠陥検出において新たな課題が生じます。技術の進歩により、製造メーカーが最終的なデバイス歩留まり(ひいては収益)を確保するために依存しているATEシステムを含む、すべてのファブ装置に対する全体的な負荷が高まっています。

半導体プロセスの微細化による性能向上の時代が鈍化しつつあることは今や周知の事実であり、ムーアの法則の軌道を維持するためには、設計、材料、パッケージングにおける革新が不可欠となっている。 半導体メーカーは、求められる処理速度を満たすために、複数の異種半導体ダイ(チプレット)や2.5D/3Dパッケージング構造など、先進的なパッケージング技術を採用している。これにより、ファブ(製造工場)には、KGD(Known Good Die:良品ダイ)やKGI(Known Good Interposer:良品インターポーザー)を確実に生産するというプレッシャーが高まっており、個々のダイがより大規模なシステムに組み込まれる前に、その性能と信頼性を検証するために、ますます高度なテスト手法が求められている。

ATE業界は、相互に関連する要因の複雑化に対応しています

テラダインは、こうした需要に先んじて対応し、前例のない課題に直面する中でも、世界の半導体エコシステムが革新を続け、繁栄し続けることを確約します。

世界の半導体業界におけるこうした劇的な変化に対応するため、当社は柔軟なテスト戦略を導入しました。これには、製造フロー全体でテストの実施タイミングを調整し、品質コストを効果的に管理する能力が含まれます。早期のテストによりスクラップコストを最小限に抑え、一方で後期段階でのテストにより徹底した品質管理を確保します。これは、データ分析を活用し、コストを削減し、歩留まりを向上させながら、テスト業務全体を通じて品質を維持するバランスの取れたアプローチです。

「シフト・レフト」と「シフト・ライト」の詳細については、

をご覧ください。

2.5D/3Dパッケージングは確かにムーアの法則を推進しますが、その経済的実現可能性は、製造の初期段階で欠陥の流出率(量産段階まで到達してしまう欠陥の数)を低減し、廃棄コストを削減できるかどうかにかかっています。プロセス内でテストを前倒しまたは後倒しにすることで、これを実現し、総コストを最小限に抑えることができます。

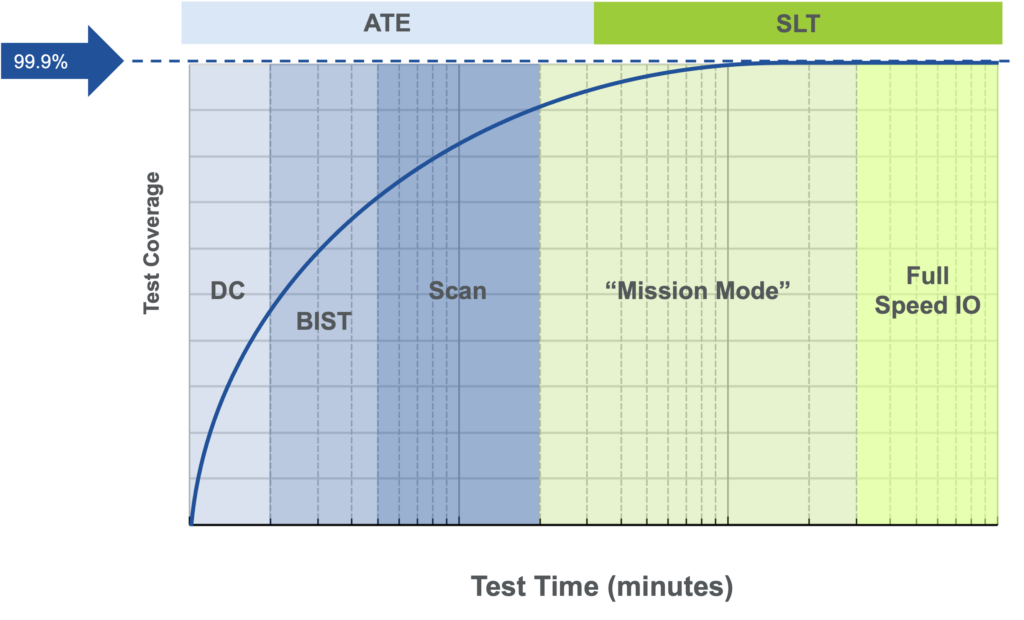

テストカバレッジを早期に拡大する手法は「シフト・レフト」と呼ばれ、ウェハー検査や部分的なパッケージングの段階で実施されることでKGDを最大化し、将来のパッケージングコストの削減に寄与する。しかし、これによりテストコストが増加する可能性があるため、スクラップ削減のメリットと慎重に比較検討する必要がある。

シフトライト戦略は、プロセスの後半においてテストカバレッジを拡大し、欠陥を検出するとともに品質を維持することを目的としています。このアプローチでは、最終段階(またはシステムレベル)のテストにおいて高い並列性を活用することで、品質目標を達成しつつコストを削減します。効率を最適化するため、高収率のテストをこれらの後半段階に移行させることができます。

目標は、製造工程全体を通じて品質と歩留まりのバランスを取り、総コストを最適化することです。具体的な戦略としては、ウェハプロービングにおける欠陥見逃し率を低減してスクラップコストを削減すること、および量産テストを効率的に実施してテストコストを削減することが挙げられます。最終的には、ダイナミックかつ継続的なプロセスにおいて、分析データに基づいて「シフト・レフト」か「シフト・ライト」かの判断が行われます。貴重なデータを活用することで、チップ製造プロセス全体を通じてテスト戦略を調整することが可能となり、テストコストを最小限に抑えつつ歩留まり率を向上させるための改善の好循環を生み出すことができます。

柔軟なテスト戦略が課題を解決

今日のダイナミックなテストカバレッジには、テラダイン社の UltraFLEXplusのようなATEと、テラダインのTitanプラットフォーム上で実行可能なsystem level test (SLT)組み合わせています。SLTは、集積半導体デバイスの最適な検証のために実環境をエミュレートし、特にシステムオンチップ(SoC)やシステムインパッケージ(SiP)といった先進技術において有用です。これにより、欠陥を効果的に特定し、コストを抑制し、データ分析を通じて歩留まりを向上させることができます。

統合前のテストにより、最終パッケージには正常に動作するダイとインターポーザーのみが使用されることが保証され、極めて効果的なKGDおよびKGIプロセスを通じて欠陥を低減します。3D積層ICについては、高度な3D-DFTテストアクセスアーキテクチャを用いて、包括的な信頼性および性能テストが実施されます。

特に重要なのは、ATEのデータ分析が、傾向や異常に関する洞察を提供することで、製造メーカーが製造プロセスをより的確に制御できるよう支援する点です。さらにAIは、これらの傾向の分析を支援し、テストパラメータの最適化や、歩留まりの向上とコスト削減に向けたリアルタイムかつ先を見越した調整を可能にします。テラダインの「Archimedes」分析ソリューションが提供するのは、 オープンな開発環境を提供し、エッジでのリアルタイム分析を可能にするとともに、 導入直後から利用可能なソリューションとカスタマイズされたソリューションの両方を柔軟に提供できる ソリューションを柔軟に提供し、容易に導入できる環境です。

同様に、データセンターの消費電力を削減することを目的としたシリコンフォトニクスにおいても、デジタル回路とフォトニクス回路の同時テスト技術の開発が不可欠です。高速データ転送と低消費電力を実現するため、フォトニクス技術が電子回路とより日常的に統合されるようになるにつれ、テストソリューションはコパッケージド・オプティクス向けに最適化されなければなりません。

次世代ATEに向けたデータ活用と自動化

今後数年間を見据えると、SiCや窒化ガリウム(GaN)といった新しい半導体材料や、集積フォトニクス向けの専用試験装置に対する需要がさらに高まると予想されます。これには、高電圧・大電流および低電圧・小電流の試験能力の向上や、単一のパッケージ内で異なる材料を効果的に扱う技術が含まれます。

ウェハーから最終パッケージに至るまで完全に自動化されたテストプロセスにより、人的介入を減らし、エラーを最小限に抑えるエンドツーエンドの自動化が、極めて重要な役割を果たすことになるでしょう。ATEは今後もAIや機械学習を活用し、テスト精度の向上、部品故障の予測、およびテストパラメータのリアルタイム最適化を図っていきます。

AIを活用したデータ分析により、パターンや傾向を特定し、先を見越した品質管理と歩留まりの向上につなげることができます。テラダインは、半導体エコシステムに特化したデータとAIによる価値創造を推進するプラットフォーム「SEMI Smart Data-AI Initiative」を通じて、業界におけるAI導入の動きを支援しています。同イニシアチブのメンバーとして、テラダインはテストデータ出力の標準化に取り組んでおり、これにより、知的財産の漏洩やベンダーロックインを懸念することなく、業界全体の連携が促進されます。

AI、最先端の半導体技術、そして地政学的動向が交錯することで、私たちの業界の未来が形作られていることは明らかです。テラダインは、柔軟かつ協調的、そして革新的なテスト戦略を通じて、半導体の信頼性と卓越性を確保することに尽力し、AIがその可能性を最大限に発揮できる未来への道筋を築いていきます。

ジョージ・S・ハルタルテ博士は現在、テラダインの半導体テスト部門においてプロダクトマーケティング担当シニアディレクターを務めています。ジョージはこれまで、テラダイン、ラム・リサーチ、ライトポイント、トランスイッチ、ロックウェル・セミコンダクターズにおいて、技術、管理、経営の各分野で様々な役職を歴任してきました。彼はIEEE 802.11 Wi-Fi標準化委員会の投票権を有するメンバーであり、IEEE 802.11ayタスクグループの幹事を務めています。 現在、ジョージ氏はIEEEヘテロジニアス・インテグレーション・ロードマップ(HIR)テスト・ワーキンググループの共同議長を務めるとともに、カリフォルニア大学サンタクルーズ校およびフェニックス大学の客員教授も兼任しています。