半導体デバイスは絶えず進歩を遂げており、データセンター向けAI・高性能コンピューティング、エッジAIデバイス、電気自動車、自動運転、携帯電話などの分野において、今日見られるような技術とイノベーションの飛躍をもたらしています。 最近の技術革新としては、オングストローム規模の半導体プロセスノード、高帯域幅メモリ、先進的な2.5D/3Dヘテロジニアス集積パッケージ、チプレット、ダイ間相互接続などが挙げられます。さらに、コパッケージド・オプティクス(CPO)形態のシリコンフォトニクスは、高性能コンピューティング用途における高速データ通信分野の重要な基盤技術となることが期待されています。

CPOとは何ですか?

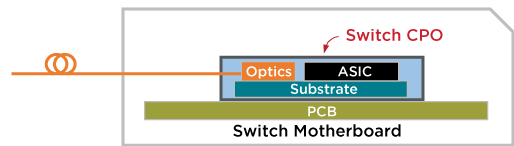

CPOは、シリコンフォトニクスチップとデータセンター用スイッチ、あるいはGPUコンピューティングデバイスを単一の基板上に統合した革新的なパッケージング技術です(図1参照)。これは、AIデータセンターアプリケーションにおいて、より高い帯域幅と速度、低遅延、低消費電力、およびデータ転送効率の向上を求める需要の高まりに対応するものです。

図1 コパッケージ化された光学部品(出典:Broadcom)

CPOを理解するには、まずその構成技術を理解する必要があります。CPOにとって極めて重要な技術の一つが、シリコンフォトニクスです。シリコンフォトニクスは、高速な光機能をシリコンチップに直接統合するための基盤技術を提供します。CMOSファウンドリ各社は、シリコン半導体技術に基づいた先進的なプロセスを開発し、シリコンウェハー上でフォトニック機能を実現可能にしました。 CPOでは、ヘテロジニアス統合パッケージング(HIP)を採用しており、これにより、これらのシリコンフォトニクスチップを、AIアクセラレータチップやスイッチASICなどの電子チップと、単一の基板またはパッケージ上で直接統合します。シリコンフォトニクスとHIPが相まって、CPO製品を実現します。したがって、CPOは、シリコンフォトニクス、ASIC、そして高度なヘテロジニアスパッケージング技術のサプライチェーンが融合したものです。

前述の通り、CPOは高速・大帯域幅・低遅延・低消費電力のフォトニック相互接続をコンピューティングの最前線にもたらします。 さらに、フォトニクスデバイスは長距離でもほぼ損失がないため、あるAIアクセラレータが数百メートル離れた別のAIアクセラレータとワークロードを共有しつつ、単一の計算リソースとして機能することが可能になります。この高速かつ長距離な相互接続を実現するCPOファブリックは、データセンターの再構築を約束するものであり、将来のAIアプリケーションの可能性を解き放つ重要なイノベーションです。

2025年現在、高度なヘテロジニアス・パッケージを用いて統合するのではなく、フォトニクス「エンジン」をスイッチやGPU ASICと同一基板上に集積させたCPOのプロトタイプが開発されている。 ここでいう光「エンジン」とは、シリコンフォトニクスチップを他のディスクリート部品および光ファイバーコネクタと共にパッケージ化したものを指し、CPOとは、複数の光エンジンをスイッチまたはGPU ASICと共に共通の基板上に実装したものを指す。

CPOの市場投入までの期間を短縮するには?

CPO向けのデータ通信市場は、通信やバイオテクノロジー分野における多品種少量生産の製品やアプリケーションなど、シリコンフォトニクス製造サプライチェーンが従来扱ってきた規模に比べて、約2桁大きい市場規模を秘めています。この大規模な生産量でCPOを実現するためには、以下の3つの要素が進展する必要があります:

- シリコンフォトニクスのサプライチェーンは、ウェハーレベルおよび光学エンジンレベルにおいて、生産能力を拡大し、高い歩留まりを達成する必要がある。

- 新しいヘテロジニアス統合パッケージングのコンセプトについては、OSAT(半導体パッケージング・テスト受託業者)やコ・パッケージド・オプティクス(COO)の受託製造業者と共同で実証を行う必要がある。

- 現在のシリコンフォトニクスの試験プロセスは手作業が多く、大量生産に対応できないため、新たな大量生産向けの試験手法を開発し、その有効性を実証する必要がある。

CPO技術はまだ成熟しておらず、大量生産段階にも至っていませんが、ウェハー、パッケージ、システムレベルのいずれにおいても、自動試験装置の試験要件に直接的な影響を与えるため、試験装置メーカーやデバイスサプライヤーはその登場に備えておく必要があります。 フォトニクス技術の急速な進歩に追随し、電気信号と光信号の両方を同時に処理できるハイブリッド試験システムを開発するためには、フォトニクス試験機能への投資が不可欠である。CPOの試験には、能動的な熱管理、高電力、大型パッケージの取り扱い、カスタムフォトニクス機器の取り扱いとアライメント、高速デジタル信号、広帯域フォトニクス信号、および高周波RF信号の試験が必要となる。

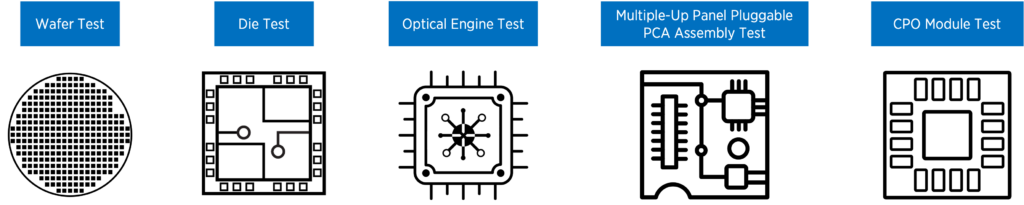

さらに、ウェハーから最終パッケージのテストに至るまで、複数のテスト工程が存在し、これらについてはテストカバレッジ、テスト時間、およびコストの観点から最適化を行う必要があります(図2参照)。運用コストと設備投資の両面で多大な製造コストが発生することを避けるためには、各テスト工程におけるテストカバレッジを最適化するための専門知識と経験が求められます。

図2:シリコンフォトニクス・ウェーハからCPOへのテスト用挿入部

CPO試験の難点

CPOデバイスの試験は、電気的および光学的の両面において多様なプロセスや材料が関与するため、特有の課題を抱えています。特に、信頼性の高い試験結果を得るために必要な精度で光学部品を位置合わせすることの複雑さが、大きな課題となっています。従来の電気信号では接続公差に多少の許容範囲がありますが、光信号は位置合わせのわずかなずれに対しても極めて敏感です。 フォトニクスと高度なデジタル処理機能を備えたコンピューティングデバイスを統合するCPOの複雑さゆえに、レーザー、導波路、および光検出器の正確な位置決めが求められます。わずかな位置ずれであっても、信号の劣化、電力損失、あるいは測定誤差を引き起こす可能性があり、テストプロセスを複雑化させます。この技術が進歩するにつれ、フォトニクスおよび光電気統合がもたらす厳格な要件に対応できるよう、自動試験装置も進化していく必要があります。

必要な精度に加え、CPOに使用される材料やプロセスもばらつきをもたらします。 異なるサプライヤーから供給された複数の光学チプレット(それぞれが異なる材料や設計を採用している可能性がある)を単一の基板に実装する場合、これら異質な要素間の位置合わせを維持することは、指数関数的に困難になります。各光学チプレットは固有の光学特性を有している可能性があるため、試験装置は、信号の送受信精度を損なうことなく、幅広い光学的な位置合わせに対応しなければなりません。これにより、様々な種類の材料や光学設計に対応し、一貫して信頼性の高い測定結果を提供できる自動試験装置への需要が高まっています。

正確な位置合わせには時間がかかるため、大量生産を行う半導体テスト環境において、大きなボトルネックとなっています。 光学部品の位置合わせは、多くの場合手作業または半自動プロセスで行われるため、テストサイクルに時間を要し、生産環境におけるスループットや効率に悪影響を及ぼす可能性があります。こうした遅延を軽減するため、自動試験装置のサプライヤーは、電気信号と光信号の両方を同時かつ効率的に処理できるハイブリッドシステムなど、高度なフォトニクス試験機能への投資を行う必要があります。また、これらのシステムには、より高速で信頼性の高い位置合わせ技術が組み込まれていなければならず、リアルタイムで調整可能なAI駆動のキャリブレーションや適応アルゴリズムを活用することが考えられます。

Testは、CPOの重要なニーズに応えます

PCIe 5.0/6.0/7.0 や 400G/800G/1.6T b/s イーサネット、さらにはそれ以上の最新業界プロトコルをサポートする、より高速なデータ相互接続への需要が高まる中、データセンターの信頼性とパフォーマンスに対する期待はますます高まっています。 データ相互接続における障害や性能の低下は、重大なダウンタイムやパフォーマンスのボトルネックにつながる可能性があります。そのため、コンポーネントがデータセンターに導入される前に潜在的な問題を特定し、対処するためのテストカバレッジの強化がますます重視されています。その結果、半導体テスト業界は、さまざまな動作条件下におけるシグナルインテグリティ、熱的挙動、消費電力など、コンポーネントの性能のあらゆる側面を網羅する包括的なテストソリューションを提供しなければなりません。

結局のところ、業界におけるCPOへの移行に伴い、テスト手法や装置の変革が求められ、特にウェハーからCPOパッケージに至るまでのすべてのテスト工程において、正確な光学アライメントが重要となります。先進的なフォトニクス・テストシステムに投資する半導体テストのリーダー企業は、この新興技術の複雑さに対処する上で優位に立ち、急速な技術進歩と高まる市場需要の両方に確実に対応できるようになるでしょう。

テラダインは、こうしたイノベーションの最前線に立ち、新技術を先取りし、半導体パッケージングおよび材料分野における最新の進歩に対応するため、柔軟かつ効果的な自動試験装置の開発に積極的に取り組んでいます。

ジョージ・S・ハルタルテ博士は現在、テラダインの半導体テスト部門において、SoC製品戦略担当シニアディレクターを務めています。ジョージはこれまで、テラダイン、ラム・リサーチ、ライトポイント、トランスイッチ、ロックウェル・セミコンダクターズにおいて、技術、管理、経営の各分野で様々な役職を歴任してきました。 ジョージ氏は、SEMI北米支部の諮問委員を務めるとともに、IEEEヘテロジニアス・インテグレーション・ロードマップ(HIR)テスト・チャプターの共同議長も務めています。 ジョージは電気工学の博士号に加え、3つの修士号(MBA、コンピュータサイエンス、電気通信)を取得しています。また、カリフォルニア大学サンタクルーズ校およびフェニックス大学の客員教授も務めています。著書に『Understanding Fabless IC Technology』があります。