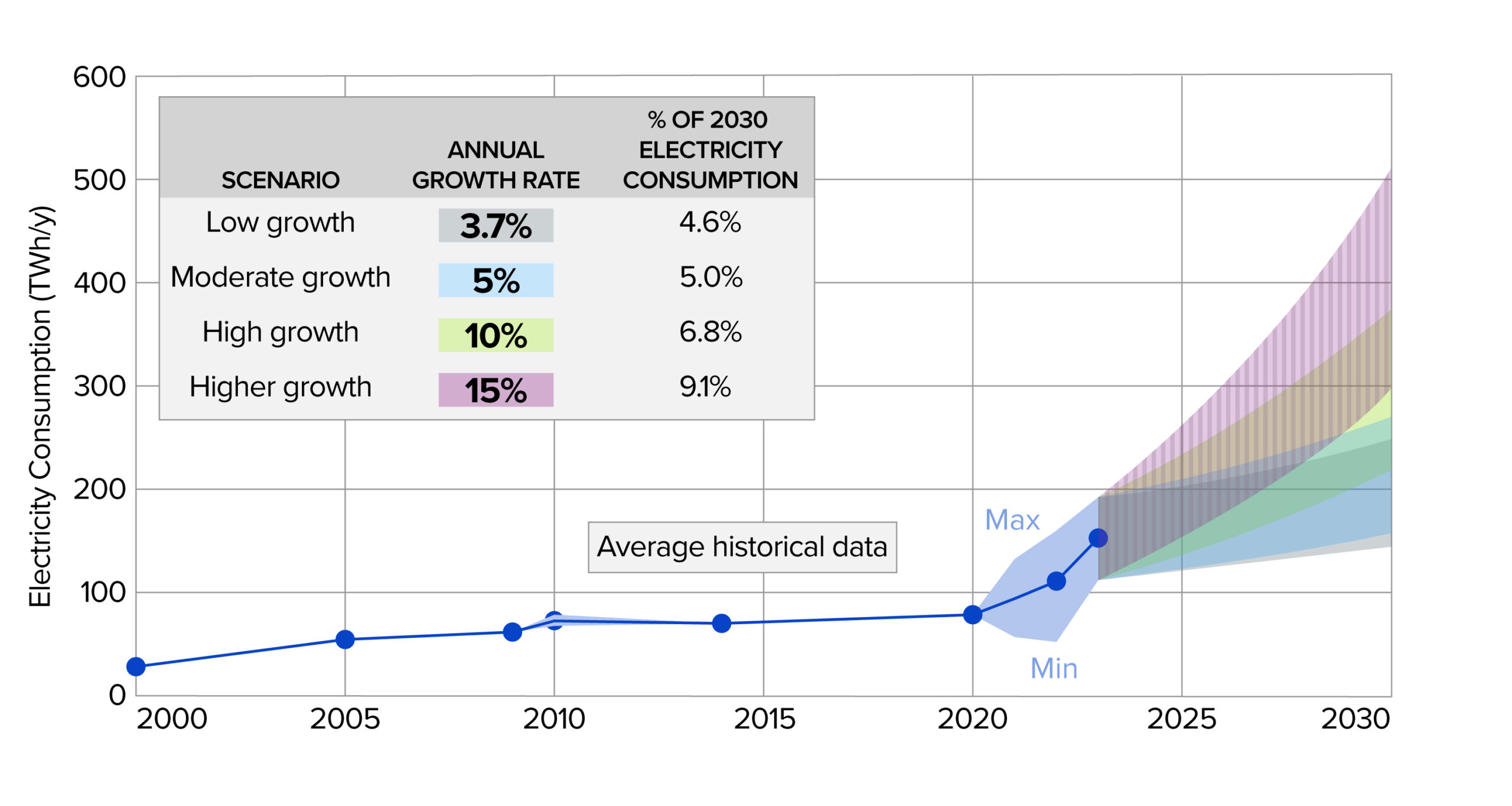

今日、ChatGPTへの1回のクエリは、従来のGoogle検索に比べて約10倍の電力を消費しており、AIが画像や動画の生成へと拡大するにつれて、この消費量はさらに増加し続ける見込みです。AIだけでなく、クラウドコンピューティングやハイパフォーマンスコンピューティング(HPC)の成長も相まって、2030年までにデータセンターの電力消費量は、米国の総電力消費量の最大9.1%を占めるようになると予測されています。

図1:米国のデータセンターにおける電力消費量の予測:2023年~2030年(出典:EPRI)

このような電力消費の急増を受け、主要なチップ設計メーカーは、エネルギー消費を削減するため、光インターコネクトソリューション、特にシリコンフォトニクス(SiPh)やコパッケージド・オプティクス(CPO)への投資を進めています。ブロードコムは、同社初のコパッケージド・オプティクス・スイッチにより30%の電力削減を実現したと報告しており、一方、NVIDIAは最近、従来のプラグイン式トランシーバーと比較して3.5倍のエネルギー効率を誇るCPOスイッチを発表しました。

シリコンフォトニクスとコパッケージド・オプティクス:接続技術の新たな時代

Silicon photonics leverages silicon to create photonic integrated circuits (PICs), which include optical modulators, photodetectors, and waveguides. These are fabricated using mature CMOS process nodes (65nm or higher), enabling faster data transfer (200G+ vs. <100G with InP or GaAs), lower power consumption, and greater bandwidth—ideal for data center and telecom applications.

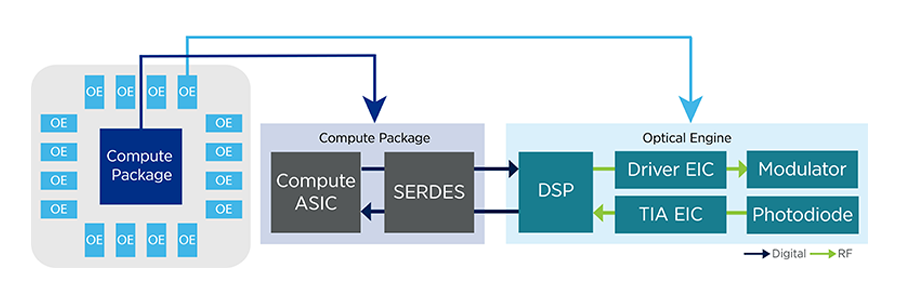

図2:16個の光学エンジンを搭載したコパッケージ型光学モジュール

コパッケージド・オプティクス(CPO)は、光トランシーバー(光エンジン)を、ネットワークスイッチ、GPU、AIアクセラレータなどのHPCデバイスと単一のパッケージ内に直接統合したものです。このアーキテクチャでは、低速で消費電力の大きい銅線リンクを光ファイバーに置き換えることで、帯域幅密度、電力効率、およびレイテンシを向上させます。 NVIDIA、Broadcom、Marvell、AMD、IBMなどの業界大手各社は、過去1年間にCPO製品の開発を発表しています。

しかし、SiPhおよびCPOの採用に伴い、新たな光学試験上の課題が生じており、これらに対処するためには、スケーラブルで大量生産可能な製造ソリューションが必要となる。

Coにおける主な課題-パッケージ済み光学部品の試験における主な課題

CPOデバイスの試験は、フォトニック集積回路のウェハレベル試験から始まり、複数の段階を経て行われます。ここでの主な課題は、光ファイバの位置合わせにおいてサブマイクロメートル級の精度を達成することです。レーザーやパワーメータに接続された光ファイバは、ウェハ上の光結合器に対して極めて高い精度で位置合わせされなければなりません。対照的に、現在の電気プローバの多くは、位置合わせ精度が数十マイクロメートル程度にとどまっています。この精度は、正確な電力測定と波長特性を確保するために不可欠です。

個体分離後、フォトニックICは、コパッケージ化されたデバイスに組み込む前に再度テストを行う必要があります。これには、ベアダイ状態でのテストや、部分的なパッケージング後のテストが含まれる場合があります。デバイスには、パッシブアライメント用の光コネクタが搭載されている場合もあれば、アクティブファイバーアライメントが必要となる場合もあります。コネクタの標準化が進んでいないことは、自動化をさらに複雑化させており、テストシステムは多種多様なコネクタタイプに対応する必要があります。

高速(または「実速度」)テストも不可欠です。一部のデバイスには自己診断機能が内蔵されており、112 Gbps または 224 Gbps の PAM4 方式でデータを生成します。これらをテストするには、TX ポートから RX ポートへの光ループバックが必要です。また、性能を検証するために、外部の高速オシロスコープやビット誤り率テスターを必要とするものもあります。

最後に、光エンジンがネットワークASIC、GPU、またはAIアクセラレータと一体パッケージ化されると、パッケージ全体をテストする必要があります。現在のCPO設計では、演算用ダイの2~4面に4~36個の光エンジンが配置されています。自動テストシステムは、すべての面で光接続を確立し、高出力レーザーを供給し、実稼働モードでのテストのための光ループバックを可能にし、数千ワット規模の熱負荷を管理する必要があります。

大量生産への拡大

プロトタイプ段階でこれらの課題を解決するだけでは不十分です。現在、プラグイン式トランシーバーの出荷台数は年間500万~1,000万台ですが、CPOの普及により、光エンジンの出荷台数は数千万台から数億台規模に拡大する可能性があります。手動またはセミカスタムのテスト手法では、この規模に対応できません。

この需要に応えるためには、光学機器やアライメントシステムを、ファウンドリやOSATのインフラとシームレスに連携する数千もの半導体自動テストセルに統合する必要があります。こうした「光電子」テストセルは、光学エンジニアだけでなく、オペレーターやサポートスタッフにとっても使いやすいものでなければなりません。SiPhおよびCPO技術の潜在能力を最大限に引き出し、次世代データセンターにおいて低消費電力と高帯域幅を実現するためには、大量生産型の自動テストソリューションが不可欠です。

テラダイン:光テスト技術の革新をリード

テラダインは、ATE、 SLT、基板レベルプラットフォームを 横断し、ウェハーレベルからコパッケージデバイス試験に至るまで、SiPhおよびCPOのライフサイクルのあらゆる段階におけるテストソリューションの開発をリードしています。テラダインは最近、シリコンフォトニクスの両面ウェハープローブ試験向け初の量産ソリューションを発表し、電気的および光学的テストプロセスの両方を効率化しました。 また、テラダインはQuantifi Photonicsを買収し、高チャネル数かつ柔軟性の高い光テスト機器をポートフォリオに追加しました。電気テストにおける深い専門知識と最先端の光技術力を融合させることで、テラダインはAIおよびHPC分野におけるシリコンフォトニクスおよびコパッケージド・オプティクスの導入を、光速で加速させています。

マシュー・グリフィンは、テラダインのオプトエレクトロニクス・テスト部門のシニア・プロダクト・マネージャーです。過去8年間、彼はシリコンフォトニクス、コパッケージドオプティクス、マイクロLED、ADASカメラインターフェース、および生産検査用マシンビジョンにおけるテスト技術の進歩を牽引してきました。