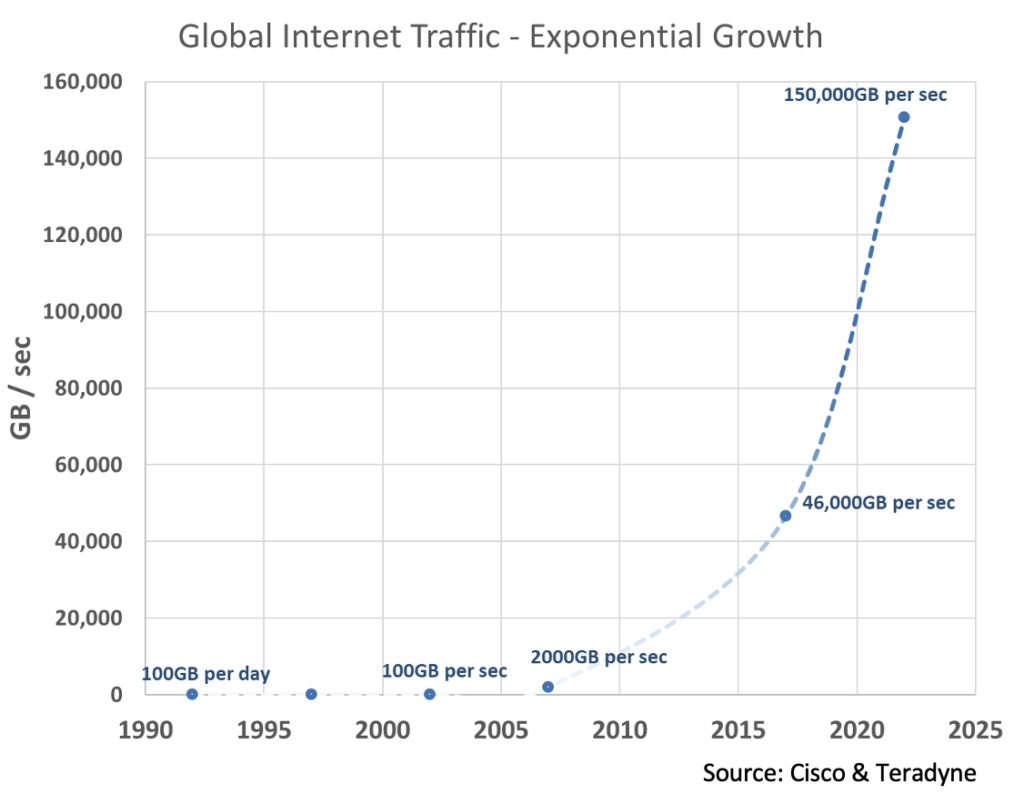

世界のインターネットトラフィックは指数関数的に増加しており、その勢いは衰える気配を見せていません。この需要が、半導体産業の進化を牽引しています。ますます増大するデータへの需要に応えるためには、データを収集するセンサー、データを転送するネットワーク、そしてデータを分析するためのストレージと処理能力が必要となります。データ需要の拡大に伴い、基盤となる技術も、現在のニーズを満たすだけでなく、将来の用途にも対応できるよう進化していかなければなりません。

新しい技術が、複雑なデジタル機器の革新を牽引している

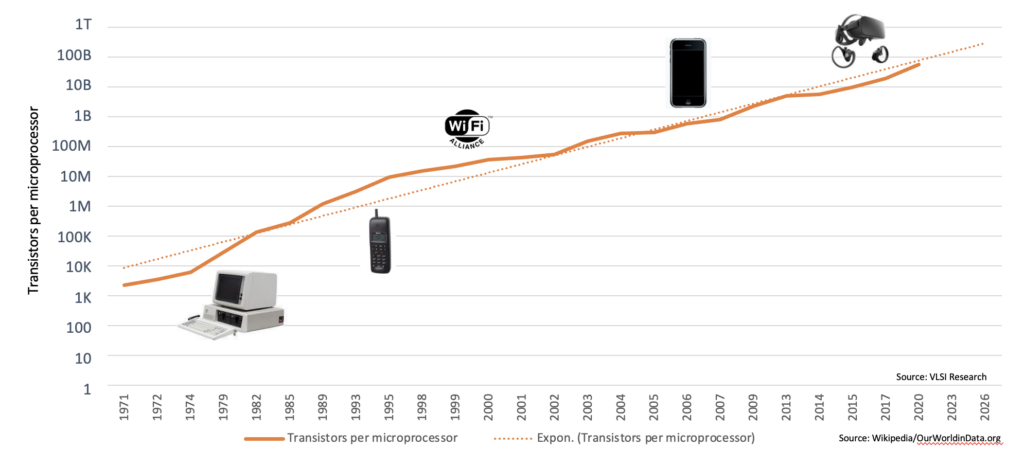

マイクロプロセッサあたりのトランジスタ数の歴史的な推移を見ると、デバイスの複雑さによって表される処理能力への需要も、過去50年間にわたり指数関数的な成長を続けてきたことがわかります。 より高い処理能力を必要とする新たなアプリケーションがこの傾向の主な原動力となっており、拡張現実(AR)のようなアプリケーションが登場する将来においても、性能への要求は高まり続けるだろう。先進プロセス技術を採用したデバイスの増加と、こうしたチップへの需要の高まりに伴い、先進的な半導体製造工場への投資額は過去1年間でほぼ倍増し、1,000億米ドルを超える新たな水準に達した。生産量の増加は高品質な自動試験装置(ATE)への需要を牽引しており、チップの複雑化が進むにつれて、試験分野においても新たな課題が生じている。

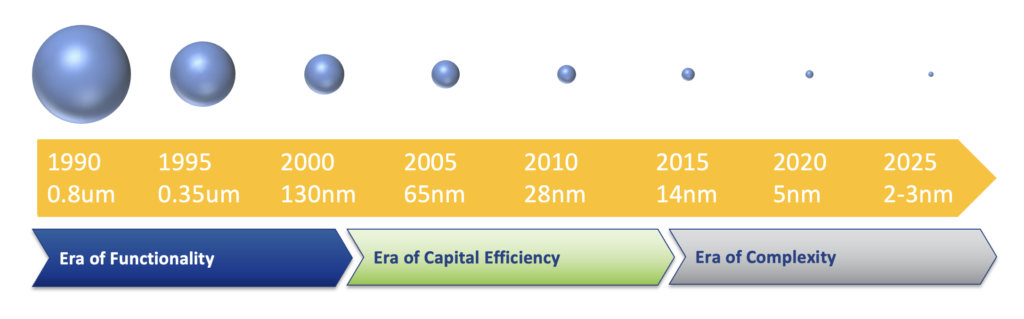

半導体テストの歴史を振り返ると、1990年代の課題は、単にデバイスの機能テストを行うことそのものにありました。次の時代では、テスト時間の短縮と並列処理能力の向上を実現した高スループットのテスト装置を活用し、コスト削減に焦点が当てられました。そしてここ数年は、半導体製造プロセスの高度化とパッケージング技術のトレンド(2011年にインテルが22nmプロセス向けにFinFETへ移行したことを皮切りに)が顕著な特徴となっています。 この傾向は、少なくとも今世紀末までは、テスト分野に影響を与える主要な要因であり続けると予想されます。

半導体デバイスの製造における最新の進展の一つとして、2次元構造から、ゲート・オール・アラウンド(GAA)FETトランジスタのような、これまで以上に複雑な3次元構造への進化が挙げられます。テストの本質は製造上の欠陥を見つけることにあるため、こうした新しく極めて微細なデバイス構造では、検出すべき微細な欠陥の種類が増え、テストの複雑さが増しています。トランジスタはますます小型化し、1つのダイ上に集積される数も増えているため、スイッチング電流も増加傾向にあります。 この点については、後ほど改めて触れることにします。

まず、トランジスタの増加がメモリ深度の拡大をもたらし、その結果として新たなデジタル試験手法が必要となり、それには新しいデジタル計測機器が求められるという事実について触れておきましょう。ただし、この点については主要なベンダー各社が早急に対応するでしょうから、ここでは、今後取り組む必要のある別のレベルの課題について見ていきましょう。

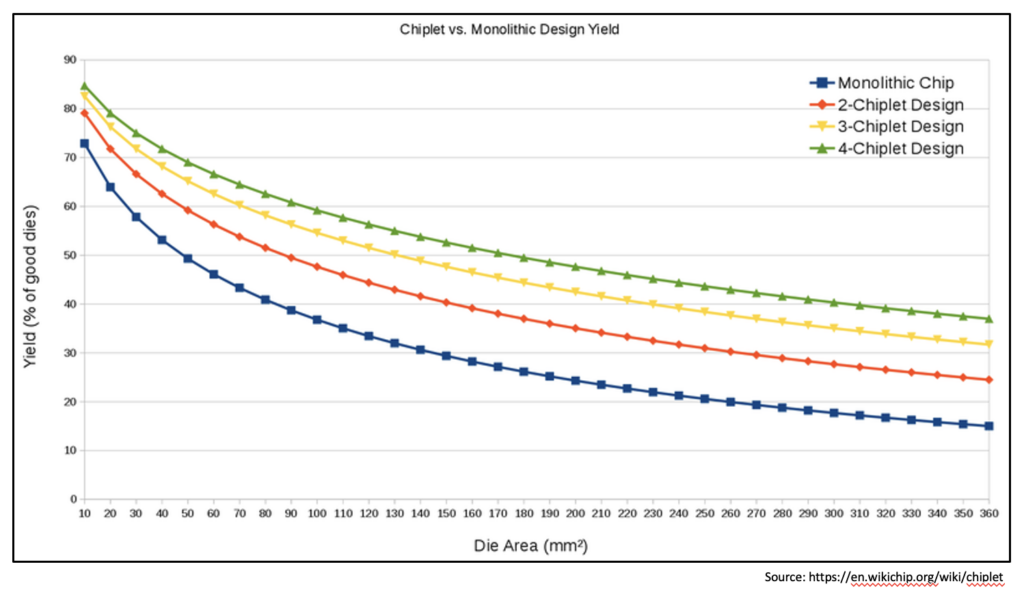

さらに興味深い課題は、ダイ上のトランジスタ数がますます増加する中で、いかにして管理可能な歩留まりを確保するかという点です。複数のダイを組み合わせることで、単一のモノリシック・ダイの歩留まりを上回る総合歩留まりが得られるというチプレットの可能性については、誰もが耳にしたことがあるでしょう。しかし、これにはテスト上の課題が伴います。その影響は、主に以下の4つのカテゴリーに分類されます:

- 品質

-

- 検証可能ではあるものの、製造時の単独状態ではテストできないように設計されたIPブロックを使用する場合、追加のダイ面積が必要になる可能性がある

- 不良ダイスの流出によるコストと、組立品の破損によるコストのバランスをとる

-

- 相互運用性:インターフェース/相互運用性テストのための効率的なテスト環境構築を可能にするため、既存のテスト規格を拡張すること。また、コスト削減を図るため、業界におけるテスト規格の採用を促進すること

- 高速インターフェース:ダイ・ループバックおよび「既知の良品ダイ(KGD)」を検証するための適切なウェーハテスト。また、コスト面からの理由により、ドライバー出力が制限された状態でバンプおよびドライバーをテストする必要性

- 高速インターコネクト:テスト装置のデジタルピンへの0.5メートルものインターフェースではなく、基板上の数ミリメートルの銅配線を駆動することを目的とした、ダイ上の高速インターコネクトおよびドライバの管理

スイッチング電流の増加に関する議論に戻ると、先進プロセスノードの採用に伴うあまり知られていない影響として、デバイスのテスター用電源への影響が挙げられます。トランジスタのオン・オフ動作は、ごく小さなコンデンサへの充電――つまり微小な充電電流――のように見えます。しかし、100億、200億、500億個ものトランジスタを合計すると、それは莫大な瞬時電流となります。 最大2000アンペアもの瞬時電流を消費するデバイスも存在しますが、プロセスノードが進歩するにつれて動作電圧は低下します。電圧が低下する一方で巨大な電流をスイッチングしなければならないというこの状況は、先進的なデジタルデバイスのテストにおける最大の課題の一つであり、そこからある物議を醸す結論に至ります。すなわち、デジタルテストにおける最も困難な課題は、実はアナログの問題であるということです。

従来の電源を使用して高帯域幅のインターフェースを構築するには、共振周波数に注意を払いながら、慎重に選定されたコンデンサを複雑に組み合わせた回路を構築する必要があります。テストエンジニアにとっての代替手段であり、唯一の実用的な解決策は、その手間を軽減し、アプリケーションのハードウェアを初回から確実に動作させるためのダイナミック電源です。デジタル・テストの本質は、最良のアナログ・ソリューションを実現することにあります。

3Dデバイス構造がシステムレベルテストの必要性を高める

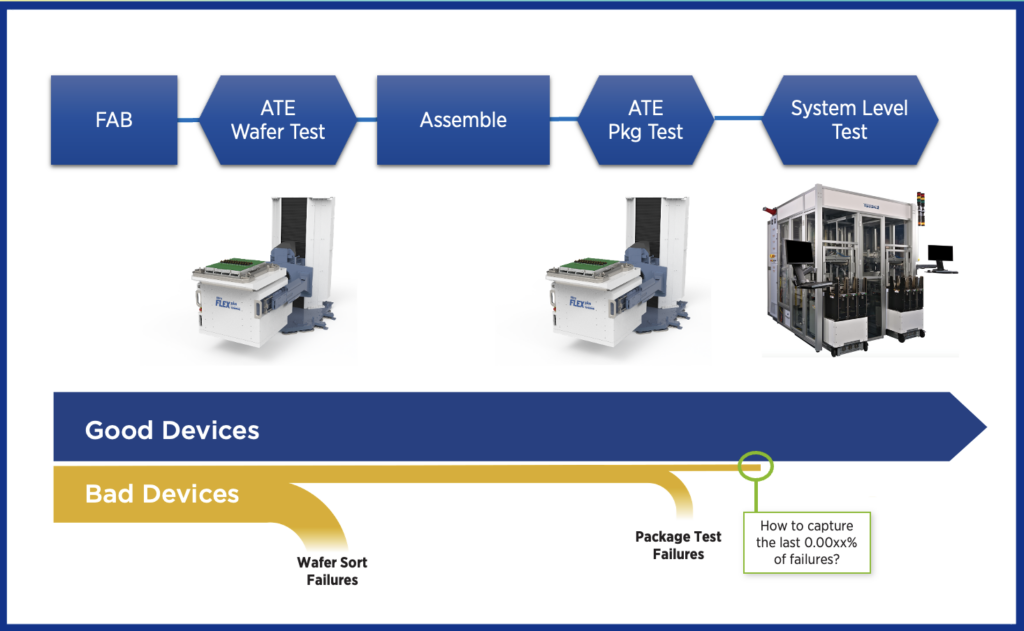

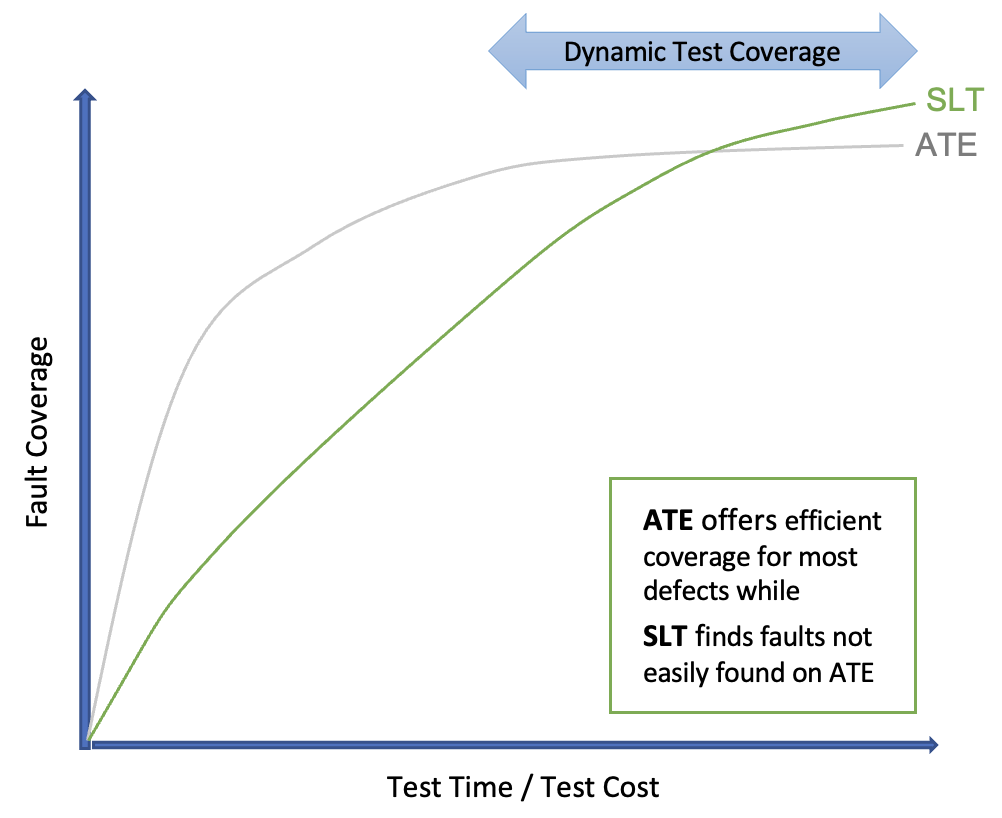

ここで、これらの複雑な3Dデバイス構造が複数の新たな欠陥モードを生み出し、従来の試験手法ではこれらの欠陥モードを発見することが極めて困難であるという事実に注目しましょう。欠陥は実動作モードでの試験においてのみ現れる可能性があり、そこで System Level Test (SLT) 装置が、先進的なデジタルデバイスにおいてますます重要性を増しているのです。

システムレベルテスト(SLT)は、従来の自動試験装置(ATE)の代替となるものでも、単に追加されるテストでもありません。ATEによる故障カバレッジは、ある程度の範囲までは迅速かつ効率的ですが、それを超えると、より微妙な欠陥を見つけるのにかなり長い時間がかかります。一方、SLTは初期段階では時間経過に伴う故障カバレッジの伸びが比較的緩やかですが、一部のより微妙な欠陥については、ATEよりも短い時間で発見できる場合があります。 将来的には、ATEとSLTの間でテストカバレッジの最適化が進むでしょう。当社の最近の動画「System Level Test 3 for 3」では、システムレベルテストのユースケースと新たなトレンドについて解説しています。

エンジニアリングの効率化による生産性の向上

高度なデジタル機器のテストにおけるこうした技術的な課題について議論するだけでなく、これが本当に半導体業界が直面している最大の課題なのか、自問すべきでしょう。リチウムやセシウムといった希土類資源の限界という現実が業界を襲っていることは、誰もが耳にしたことがあるでしょう。しかし、歴史的に見れば、材料不足を補うための代替技術は常に開発されてきました。そこで、この業界におけるもう一つの希少な資源――すなわち「エンジニア」について考えてみましょう。 優秀なエンジニアの不足と業界の急激な成長を背景に、人的資本が業界の成長ポテンシャルに与える影響を最小限に抑えるための戦略を検討することが不可欠です。

現在、希土類鉱物に対して取られているアプローチ――つまり採掘による生産量の拡大――を参考にすることができるでしょう。教育機関に生産量の拡大を要請することも可能です――実際、彼らはすでに取り組んでいます――が、それには時間がかかります。おそらく私たちに残された時間よりも、もっと長い時間がかかるでしょう。

人工知能もまた、注目のトピックの一つです。比較的短期間で大きな進歩を遂げており、将来的には標準的で反復的な作業を自動化することで、エンジニアのコード生成を支援するようになるかもしれませんが、近い将来、AIがエンジニアを完全に置き換えることはまずないでしょう。

しかし、既存のエンジニアの業務効率を高め、生産性を向上させることは可能です。今日のテストエンジニアは、設計から量産開始までのリードタイムを短縮し、さらにスループットと歩留まりを最大化するという絶え間ないプレッシャーに直面しています。このプロセス全体には複雑さがつきものですが、その複雑さを最小限に抑えるソリューションを選択することで、生産性を大幅に向上させることができます。テラダインの製品はこうした点を念頭に置いて設計されており、市場投入までの時間を短縮し、歩留まりを最大化する革新的なソリューションを提供しています。

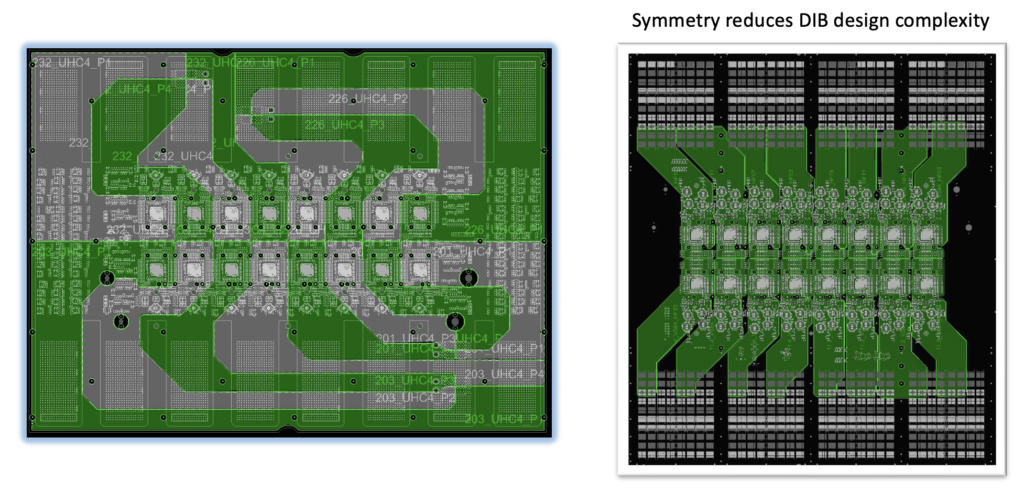

まずは、テストエンジニアの業務の複雑さを軽減することから始めるのが良いでしょう。もし、各サイトが同じ対称的な設計を採用できるように設計されたテスターがあればどうでしょうか。そうすれば、マルチサイト用インターフェースボードが不要になり、結果としてDIB(デバイス・インターフェース・ボード)の設計の複雑さを軽減できるはずです。これにより、設計工数が削減され、サイト間の整合性が大幅に向上し、設計が根本的に簡素化されるため、テストエンジニアはテストリストや被試験デバイスそのものに集中できるようになります。

テラダインのBroadsideアプリケーションインターフェースは、 UltraFLExplus はまさにこれを実現し、DIB回路用の広いPCB領域を(PCBの端に追いやられるのではなく)計測器接続部とDUTの間に配置することを保証します。これにより、サイト間の配置をコピー&ペーストすることが真に可能となり、レイアウトの一貫性が確保されます。 この簡便性により、テストエンジニアのDIB設計時間が短縮されるだけでなく、さらに重要な点として、複数サイト間の不具合によるデバッグ時間の長期化、あるいはサイト間の設計不整合によるDIBの再設計といったリスクを回避できます。 マルチサイト間の性能を一致させつつ相関分析の時間を短縮することで、Broadsideインターフェースは、量産対応のテストプログラムを作成するためのエンジニアリング工数を20%以上削減し、テストセル数を15%~50%削減することで製造生産性を向上させます。アーキテクチャを単純化することで、エンジニアの生産性が向上します。

データもまた、工場の生産性を向上させるために活用できる分野の一つです。 場合によっては、テストフローに沿った低遅延かつ迅速な意思決定が必要となり、テスターと緊密に連携したローカルソリューションが求められます。一方、その他のデータ処理については、クラウドや工場のMESシステムに送信する必要があります。こうしたデータは、顧客のソフトウェアシステム上で処理されることで、データ分析に基づいて決定されたアクションが製造プロセスの他の部分にも影響を与えるようにする必要があります。効率向上においては、エッジ分析とクラウド分析の両方が重要な役割を果たします。

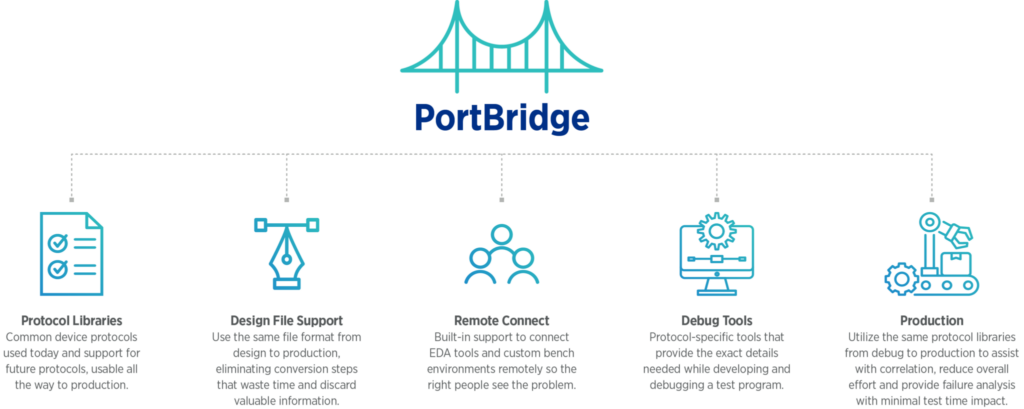

エンジニアの効率を高めるもう一つの方法は、非効率が生じている箇所を特定することです。設計部門とテスト部門は異なる言語で業務を行っており、それぞれの分野のエンジニアは、相手には理解できないような話し方をしがちです。多くの問題では、テスト結果が設計チームに送り返され、検討やテストベクトルの修正を経て、再びテスターに戻される必要があります。このデバッグのループには、数時間、場合によっては数日もの時間がかかることがあります。Teradyne社のPortBridgeのような、これらの領域をつなぐブリッジは、情報の流れを効率化し、設計エンジニアやベンチエンジニアがATEと直接通信してデバッグを行えるようにするとともに、テストエンジニアがフラットパターン上の不具合を理解・診断できるようにします。かつては数週間、あるいは数ヶ月を要していたプロジェクトが数日に短縮され、運用において大幅な工数の削減が可能になります。

高度なデジタル技術は新たな技術的課題を生み出しており、半導体産業の成長を阻害しないためには、これらに対処する必要があります。技術は常に、要件や需要に応えるべく進化し続けるでしょう。ここではこうしたトレンドのいくつかを論じてきましたが、最も効果的な解決策のいくつかは、エンジニアの生産性を大幅に向上させるツールを提供することです。当社のエンジニアは需要の高い貴重な人材であり、彼らの生産性を高める先進的なツールと機能を提供することが、今後も飛躍的な成長を実現し続けるための鍵となるでしょう。

先進プロセスノード向けのテラダインのテストソリューションについて、詳しくは弊社までお問い合わせください。

リーガン・ミルズは、テラダインの半導体テスト部門において、マーケティング担当副社長兼SOC事業ユニットのゼネラルマネージャーを務めています。テラダイン入社以前は、オートメーション・エンジニアリング・インコーポレイテッドおよびアークティック・サンド・テクノロジーズで管理職を歴任しました。マサチューセッツ工科大学(MIT)で電気工学およびコンピュータサイエンスの理学士号を、ボストン大学で電気工学、制御システム、デジタル信号処理、アナログ設計の理学修士号を取得しています。