半導体トランジスタの微細化が進み、チップの複雑さが飛躍的に増大する中、高品質な製品のみを市場に送り出すためには、半導体テストが不可欠となっています。許容品質水準(AQL)の基準がより厳格化されるにつれ、これらの基準を満たすためにテスト手法も絶えず進化させなければなりません。システムレベルテスト(SLT)と自動試験装置(ATE)を用いた従来のテストを組み合わせることで、デバイスが品質要件を確実に上回ることを保証する包括的なテスト戦略が実現されます。

多くのテスト上の問題を特定・解決できるシステムレベルテスト(SLT)は、決して新しい技術ではありません。1990年代後半からコンピュータ分野で利用されてきました。しかし、チップに集積されるトランジスタ数が飛躍的に増加するにつれ、チップの複雑さは増しており、集積回路(IC)メーカーの間で、チップの歩留まりと品質を向上させるためにSLTを採用する動きが広がっています。

システムレベルテストとは何か、そしてなぜ他と異なるのか?

システムレベルテスト(SLT)は、機能テストとも呼ばれ、被試験装置(DUT)を実際の使用環境下でテストする手法です。オペレーティングシステムを起動し、被試験装置を使用して一般的なアプリケーションテストや特定のアプリケーションテストを行うことで、従来の自動試験装置(ATE)によるテストでは得られない追加の検証を行うことができます。SLTテストは、通常、通常の装置動作に追加の検証手順を加えたものです。

システムレベルテストを推進する業界動向

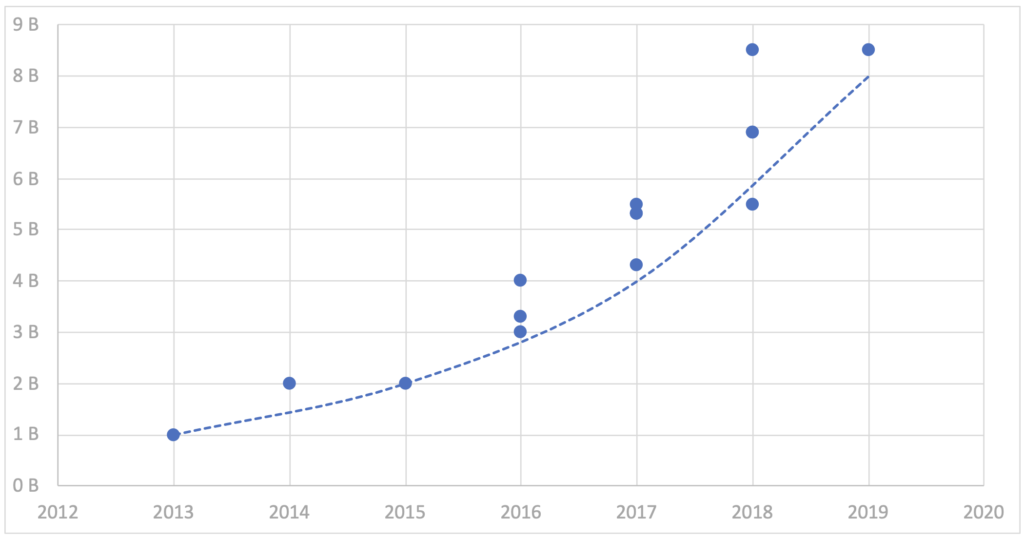

過去20年間、半導体業界におけるいくつかの動向により、SLT市場は著しく成長してきた。

まず、デバイスの品質に対する要求が高まっています。過去10年間で、人々は携帯電話やその他の電子機器への依存度を高めており、その結果、チップの品質に対する要求もますます高まっています。これにより、メーカーは、エンドユーザーが製品購入後に問題に直面する可能性を低減するため、チップやシステムに対して包括的なテストを実施するようになっています。こうした背景から、モバイルデバイス向けのSLTは急速な成長を遂げています。

もう一つのトレンドは自動車分野に見られます。自動運転支援車では、電子デバイスやソフトウェアを用いて状況を感知し、自動ステアリングや自動ブレーキで対応します。先進運転支援システム(ADAS)にはより高い基準が求められるため、超高出力デバイスやミックスドシグナルデバイスの性能、さらにはプラットフォームの効率性や熱的安定性が極めて重要となります。

チップサプライヤーは、性能、バッテリー駆動時間、および歩留まりを向上させるため、技術の限界に挑戦し続けています。つまり、彼らは以下のことを行わなければなりません:

- プロセスノードの変更に伴う製品のリリース時期を、プロセス不良率が高くなる可能性があるとしても、可能な限り早める

- バッテリーの駆動時間を延ばすため、できるだけ低い電圧で動作させてください

- 歩留まりを最大化するために、位相ロックループ(PLL)の設定を微調整する

- 最先端のパッケージング技術を採用し、トランジスタの高密度化と性能向上を図る

さらに、自動車用インフォテインメント分野においても、自動車メーカーはかつてないほど技術の最前線に近づいています。最先端技術を採用して安定性を高めることで、自動車用インフォテインメント製品の市場投入までの期間を短縮することが可能になります。

SLTのもう一つの成長分野は、ビッグデータ処理やエッジ・クラウドAI(人工知能)アプリケーションであり、これらには数百ワットから数千ワットに及ぶ高電力が求められます。

これらの多様な市場を牽引する要件は多岐にわたるため、完成品に高品質な部品が確実に組み込まれるようにすることは、極めて重要であると同時に非常に複雑な課題となっています。技術が常に限界まで追求される中、欠陥の見落としを防ぎ、部品が所定の品質基準を満たすことを保証する上で、SLTの活用はますます重要になっています。製品品質の向上に加え、装置を最終用途に可能な限り近い場所で稼働させることは、市場投入までの期間を短縮することにも寄与します。

従来のテストカバレッジの確保がますます困難になっている

ICメーカーは、1つのチップにますます多くの機能を統合し続けています。モバイルプロセッサを例に挙げましょう。初期の頃は、その機能は主に通話に限られていました。しかし現在では、モバイルデバイスはグラフィックス、画像処理、高度なセキュリティ機能などをサポートしています。かつては通信はデジタル処理によって行われていましたが、今日のデバイスには音声や生体認証データの処理、さらにはAIアルゴリズムまで組み込まれています。そのため、アプリケーションプロセッサ(AP)は高速メモリと統合される必要があります。

プロセッサは時とともに進化を続け、その機能も急速に拡大しています。健康指標の追跡、記録・保存、接続・制御、安全確保のための車載周辺センサーとの通信、さらには機械学習やAIによる生活の利便性向上といった機能は、生産性と安全性を絶えず高めています。これらの機能ブロック間の相互作用に起因する不具合は、特に各ブロック内のテストインターフェースが異なる言語を使用している場合、特定が極めて困難となる可能性があります。

すべて これらの これらすべての新機能が1つのAPに統合されており、 つまり トランジスタ数の増加を意味します 、場合によっては 上回るムーアの法則の トランジスタ数の増加を意味し、場合によっては

もちろん、テストにおける課題はデバイスの機能だけにとどまりません。ICに多数のトランジスタを集積する際、トレードオフが生じることがあり、その結果、従来の方法では達成できたテストカバレッジが低下してしまうことがあります。トランジスタ数の増加に伴い、故障の発生確率も高まるため、故障率の上昇を防ぐには追加のテストが必要となります。ATEテストだけではすべての故障を検出できなくなっているため、より包括的なテストカバレッジを実現するためにSLTを活用することができます。

SLTの実行方法

SLTは、製品の最終用途に極めて近い条件下で行う機能試験です。「システム」部分は、専用のシステムレベルテストボード上で実装され、試験フローには以下が含まれます:

- 特定の操作の実行: デバイスの汎用機能およびシステムに組み込まれたターゲットアプリケーションを実行し、それらが期待どおりに動作することを確認します。これらの操作には、チップの起動、オペレーティングシステムのロード、またはパフォーマンス評価プログラムなど、モジュールによって作成された特定のプログラムの実行が含まれます。使用されるシステムレベルテストボードは、顧客に提供されるリファレンスデザインや評価ボードと同様のものです。

- 操作が成功したかどうかの判定:テスト結果や操作の成否に基づいて測定される。例えば、内部プロセスが正常に実行されたかどうかを検証する場合、オペレーティングシステムが正常に起動できることを確認するか、特定の値(例:パフォーマンステストの結果と閾値の比較)を測定し、それを判断の根拠とする。

多くの場合、SLTのシステムには、テストフローを実行するためのオンボードプロセッサが搭載されています。SLTは主にシステムオンチップ(SoC)およびシステムインパッケージ(SiP)チップを対象としているため、テストプロセッサは通常、被試験デバイス(DUT)の一部となっています。そうでない場合は、被試験デバイスの周辺テストシステムに適切なプロセッサを搭載する必要があります。

被試験デバイス周辺のSLT基板回路は、要件に応じて変更される場合があります。 故障エスケープレポートは、画面上に迅速かつ簡単に表示できます。この種のテストは、機能的な故障をトランジスタレベルまで追跡するために多大な故障解析を行う必要があるため、ATEでは実現が困難です。SLTは、故障を誘発する正確なユースケースを使用でき、この機能テストをSLTテストに迅速に追加できるため、この種のテストに適しています。これにより、故障エスケープの根本原因をほぼ即座に特定することが可能です。

しかし、SLTはATEで見られるような構造試験ではなく、実際の端末の使用シナリオをシミュレートする機能試験であるため、SLTの試験時間は通常、従来のATEよりも長くなります。そのため、SLTの費用対効果を維持するには、並列試験の効率が重要となります。ATEの試験時間は通常10秒単位であるのに対し、SLTの試験時間は1分から10分単位となります。 最高の効率を実現するためには、並列テストの効率がATEよりも1桁以上高くなければなりません。

コストは重要

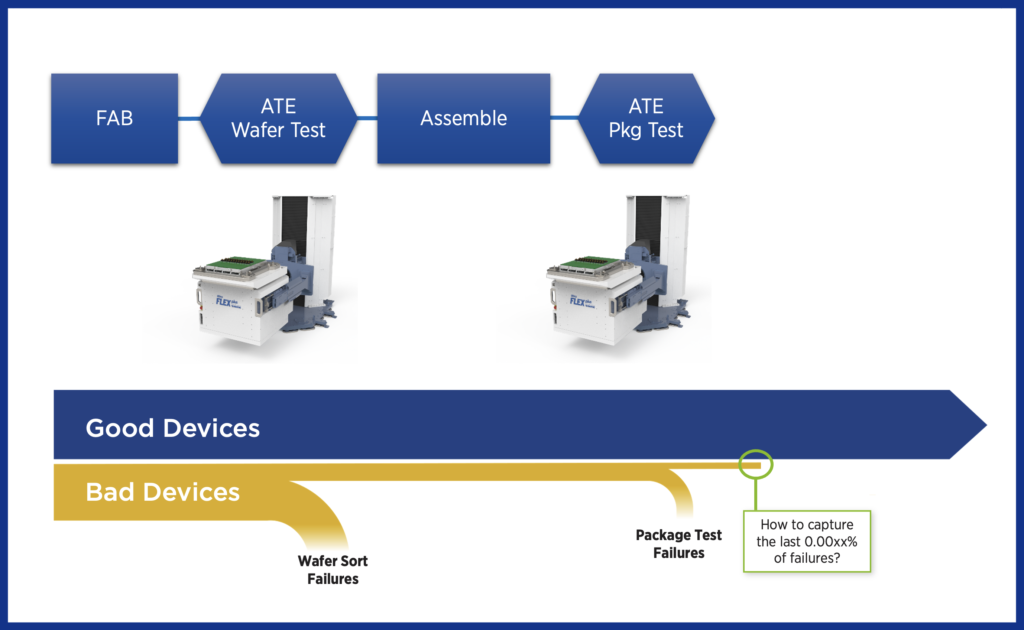

結局のところ、コストは重要な要素です。包括的なテスト戦略を策定することで、欠陥を可能な限り早期に検出でき、下流工程でのコスト増を回避できます。ATEウェハテストは、トランジスタレベルの問題、周波数や電圧レベルの変化に対する感度、および基本的な設計仕様の適合性など、プロセスの初期段階で欠陥を検出する上で高い効果を発揮します。

パッケージング工程で発生する不具合もあり、ATE最終検査ではこうした問題を特定します。しかし、非常に微細かつ複雑な不具合も依然として存在するため、欠陥率(DPPM)の低さが求められる場合、そのデバイスは検査の合格基準をクリアできないことがあります。

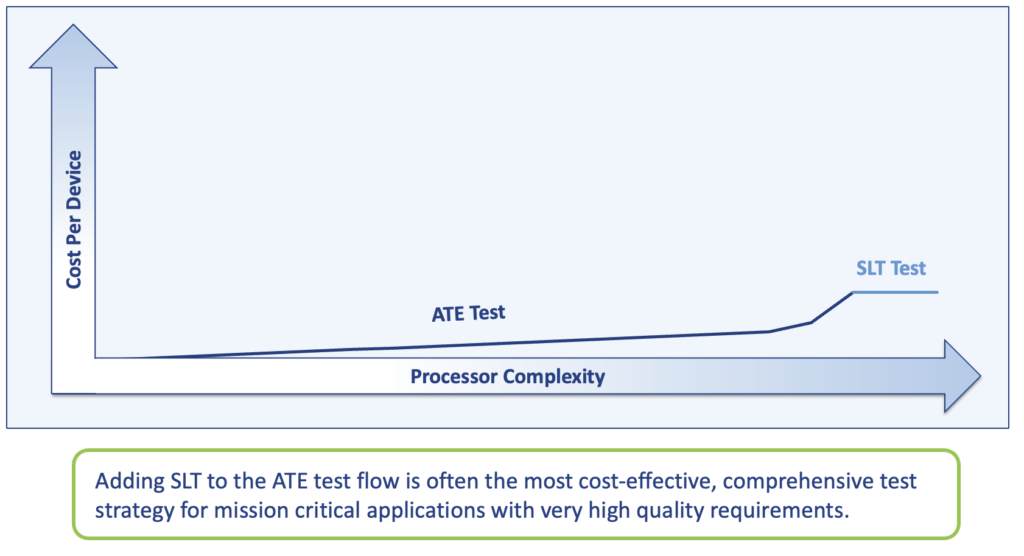

従来の品質要件の場合、ATEのコストは通常、テスト時間が長くなるにつれて増加します。この増加は概ね制御可能であり、ある程度は直線的な傾向を示します。しかし、高度に複雑なトランジスタ出力が必要となる場合、ATEのコストは最終的に曲線の変曲点に達し、指数関数的に増加することになります。

これは主に、これらの不具合の特定に多大な時間を要すること、また周辺機器を用いたテストが必要となるためです。現在、これらのテストの一部は、パラメータテストや機能テストを含め、ATE上で実施されています。しかし、追加回路の数やテスト時間が長くなる場合、この種のテストをATEで行うことは現実的ではありません。 興味深いことに、SLTのコストやテスト時間は、単にアプリケーションを起動または実行するだけであるため、複雑さが増しても増加しません。過去50年間、ATEはトランジスタレベルの設計パラメータの欠陥を捕捉する上で非常に優れた性能を発揮しており、今後もそのための最も費用対効果の高い方法であり続けるでしょう。SLTは、実世界のチップアプリケーションシナリオを用いてATE上で実装できないテストに使用すべきです。

なぜ多くのクラスの故障はATEでは検出されるのに、SLTでは検出されないのでしょうか。その理由は、ATEとは異なり、SLTはすべてのトランジスタとそのパラメータを体系的にテストするのではなく、デバイスにおける実世界のアプリケーションの一部のみをテストし、機能的な結果を提供するからです。考えられるすべてのアプリケーションプログラムを実行して、すべてのトランジスタを駆動し、故障を発生させることは、ほぼ不可能です。

SLTの費用対効果は、ATEではテストできない問題に起因する故障の一定割合を検出するためにSLTを活用すること、あるいはチップとその周辺の複数のIPモジュールを同時に刺激することで実現されます。同時テスト可能数(一度にテストできるデバイスの数)がATEに比べてはるかに多いため、デバイス1台あたりのテストコストはATEの4分の1以下に抑えることができます。

複雑さが飛躍的に増し続け、ミッションクリティカルなアプリケーションの数も増え続ける中、ATEとSLTのテストを組み合わせることは、最小限のコストで高い品質レベルを維持するための理想的なソリューションです。

ある程度、ATEのコストは回路の複雑さやトランジスタ数に比例するため、ウェハーレベルやICレベルでの欠陥検出に活用すべきです。SLTは、テストフローの最終段階で、検出が困難な残りの少数の欠陥をスクリーニングするのに非常に費用対効果が高い手法です。したがって、品質要件が極めて高いミッションクリティカルなアプリケーションにおいては、既存のATEテストフローの最後にSLTを追加することが、多くの場合、最も費用対効果の高い戦略となります。

なぜテラダインなのか?

ATEとSLTの両方を活用して初めて、包括的なテスト戦略を確立することができます。必要な品質レベルやコストなど、さまざまな要素を考慮することで、企業はATEとSLTの最適なバランスを見極めることができます。

Teradyne Titan™ SLTテスターの利点の一つは、真の並列テスト機能です。各チップは隣接するチップと完全に独立しているため、SLTやバッチ処理をより効率的に実行できます。

さらに、テラダインは10年以上にわたり運用されている大規模な自動生産プラットフォームを有しています。当社のストレージ自動化アーキテクチャと半導体テストの専門知識を融合させることで、「Teradyne Titan」は包括的なSLT自動化およびテストソリューションを提供します。

SLTは、所定の品質基準を満たしていることを確認するための、ATEテストを補完・拡張するテスト工程です。テラダインは、テストライフサイクル全体をサポートするソリューションを提供しており、お客様がテストカバレッジを最大限に高め、市場に最高品質の製品を投入できると同時に、テスト時間とコストを削減できるよう支援します。

結論

SLTは30年近く前から存在しており、主に最先端の大規模デジタルコンピューティング用途に用いられています。一部の不具合は実際のアプリケーション環境でのみ確認できるものですが、SLTはこの点において特に適しています。これは、システムレベルテストボード上のチップに対し、専用の周辺機器を用いてアプリケーションレベルでのテストを行うもので、最後の0.00xx%の不具合を捕捉し、エラーの検出漏れ率を可能な限り低く抑えることを目的としています。

SLTの成長は、品質に対する要求の高まり、電子機器の応用分野の急速な拡大、チップの複雑化、および市場投入までのリードタイムの短縮によるものです。テラダインは、ATEとSLTテストを組み合わせることで、大量生産向けの包括的なテストソリューションを提供しています。このソリューションは、可能な限り多くの欠陥を検出することを目的としており、携帯電話向けアプリケーションプロセッサだけでなく、自動車やハイパフォーマンスコンピューティングといったエンドマーケット向けのプロセッサにも対応可能です。

ぜひ読み進めてください ― 当社の「システムレベルテスト」に関するホワイトペーパーをご覧ください。

テラダインのSLTおよびATEソリューションについて詳しく知りたい方は、お問い合わせください。

ナタリアン・Z・ダーは、テラダインのビジネス戦略およびシステムレベル・テスト・マーケティング担当ディレクターです。ナタリアンは2018年にテラダインに入社し、UltraFLEXplus の管理および中国戦略の統括を担当しています。テラダイン入社以前は、サムスン傘下のハーマンにおいて、カーアフターマーケット・エレクトロニクス製品ラインのグローバル製品ライン管理担当シニア・ディレクターを務めていました。 ナタリアンはキャリアをシリコン・ラボ(Silicon Labs)でスタートさせ、携帯電話および自動車市場向けの放送用RF ICの管理を担当しました。ナタリアンは、テキサス州ヒューストンのライス大学で電気工学の修士号および経営学修士号を取得しています。