集積回路上のトランジスタ数がおよそ2年ごとに倍増するという「ムーアの法則」は、コンピューティング技術の進歩にとって極めて重要です。数十年にわたり、ファブ(半導体製造工場)はトランジスタを極限まで微細化することで、デジタル性能とトランジスタ密度の飛躍的な向上を実現してきましたが、こうしたプロセスの物理的限界に直面しています。 今日、新しいプロセス技術やチプレットのような先進的なパッケージングソリューションにより、業界はムーアの法則に基づく処理能力とデジタルスケーリングを継続することが可能になっています。早くも1965年、ゴードン・ムーア自身も次のように指摘していました。「個別にパッケージ化され、相互接続された小さな機能から大規模なシステムを構築する方が、経済的であるかもしれない。」

近年、チプレットの普及が進んでいるものの、設計、製造、パッケージング、およびテストの各段階において、依然として多くの課題に直面しています。そのため、所望の歩留まり目標と品質水準を達成しつつ、欠陥の混入率とテストコストを引き続き低減するためには、設計・製造・テストのループを最適化することが不可欠です。

品質総コストの最適化は極めて重要である

KGD(既知良品ダイ)テスト、最終テスト、システムレベルテストといったより複雑なテストプロセスに取り組む際には、品質総コストを最適化する戦略が極めて重要となります。考慮すべき主なポイントは以下の通りです:

- 設計プロセスの初期段階において、設計者とテストエンジニアは、チップの検証や不具合のデバッグを行うために、共通のツールを使用して連携する必要があります。

- テストの一部をプロセス全体の早い段階に前倒しすることで、KGD統合前の不具合を削減できる

- 製造工程の後半に一部の検査を延期することでコストを削減する

- 製造プロセスが成熟し安定するにつれ、大量生産の前および生産中に分析手法を活用して検査プロセスを調整することで、品質維持にかかる総コストを最適化できる

欠陥の見落としが莫大な廃棄コストを招く

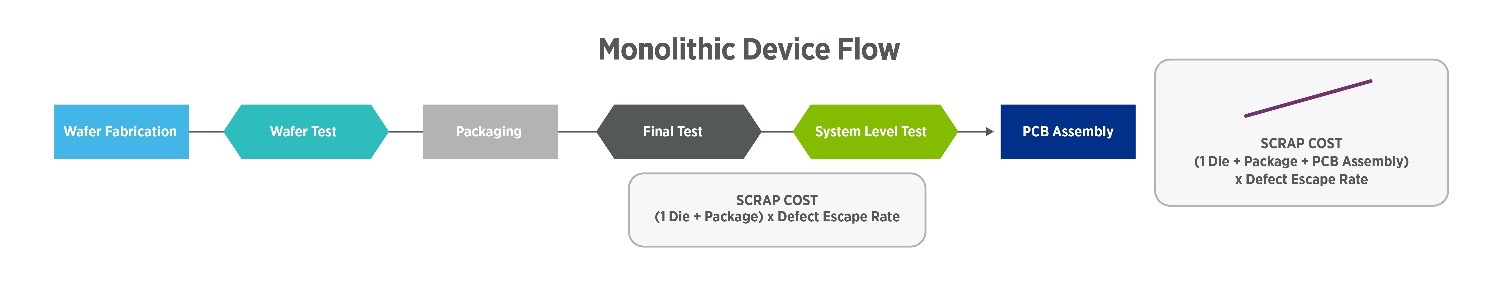

従来のモノリシックデバイスと比較すると、チプレットの設計および製造プロセスは大きく異なります。従来のモノリシック半導体デバイスの製造に伴う廃棄コストは、単一チップのコスト、パッケージング、および組立コストを含め、基本的に線形です。

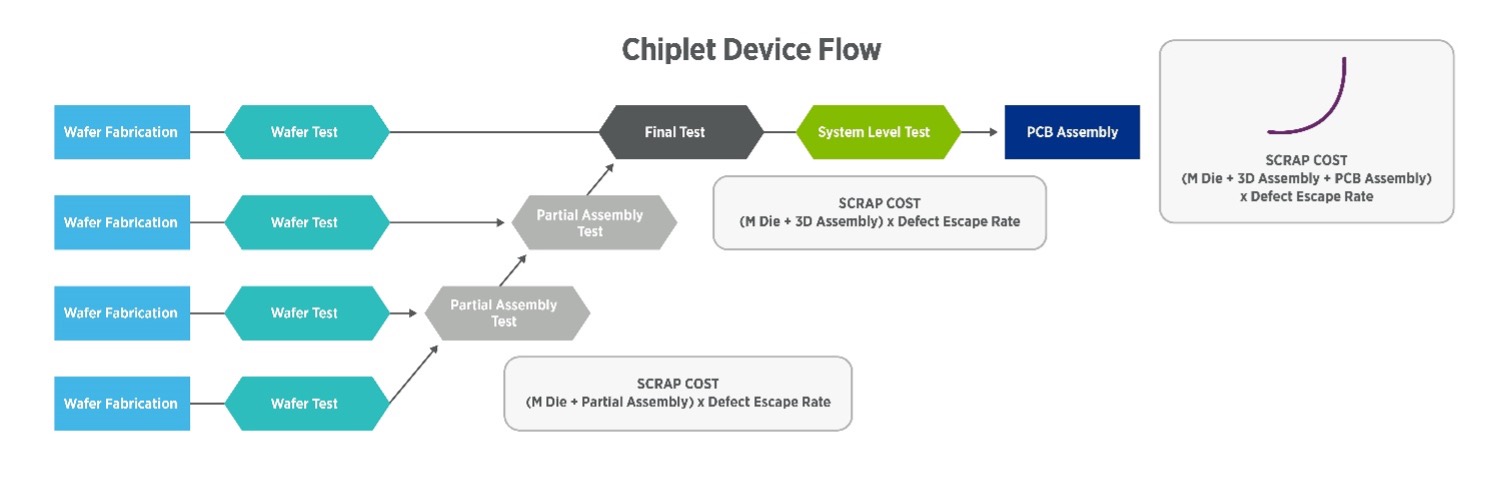

2.5D/3D設計の製造プロセスでは、スクラップコストの累積において大きな違いが見られます。具体的には、複数のダイ、マルチチップ部分アセンブリ、および/または完全な2.5D/3Dパッケージに伴うスクラップコストにより、製造から組立に至るまで、これらのコストは幾何級数的に増加します。

2.5D/3D設計の製造プロセスでは、スクラップコストの累積において大きな違いが見られます。具体的には、複数のダイ、マルチチップ部分アセンブリ、および/または完全な2.5D/3Dパッケージに伴うスクラップコストにより、製造から組立に至るまで、これらのコストは幾何級数的に増加します。

「シフト・レフト」か「シフト・ライト」か?

2.5D/3Dパッケージングは次世代のムーアの法則を実現する鍵となる技術ですが、このアプローチの経済的実現可能性を確保するには、製造工程の初期段階で欠陥の流出率を低減し、不良品コストを削減する必要があります。 テスト工程における「シフト・レフト」または「シフト・ライト」は、これらの目標を達成し、2.5D/3Dデバイスの総製造コストを最小限に抑えるための戦略である。「シフト・レフト」とは、製造プロセスの早い段階(例えば、ウェーハ検査や部分的なパッケージング工程中)でテストカバレッジを拡大し、KGD(合格率)を最大化すると同時に、将来のパッケージングコストを削減する手法である。また、新たな故障タイプや故障モードを特定するために、プロセスに追加のテストを導入することも可能である。

しかし、「シフトレフト」のメリットについては、慎重に検討する必要がある。例えば、製造プロセスの初期段階でテストの頻度を高めることは、正常なデバイスにはプラスの効果をもたらすが、その結果生じるスクラップコストの削減分を考慮しても、最適化による効果だけでは十分に相殺できないほど、テストコストの増加につながる可能性がある。

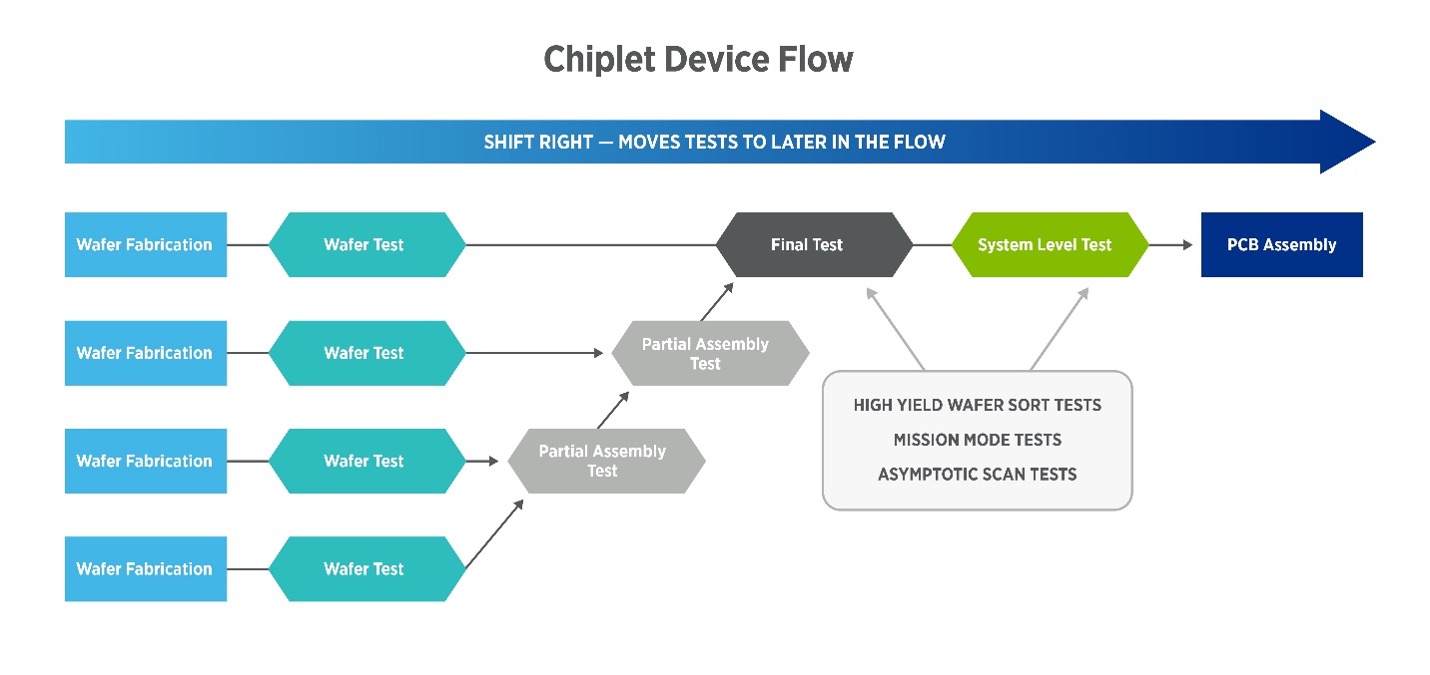

右にシフト これは、製造プロセスの後半段階でテストカバレッジを拡大し、欠陥を検出する能力を高め、品質レベルを維持することで、テストの並列化を強化し、コスト削減を図ることを意味します。

右にシフト これは、製造プロセスの後半段階でテストカバレッジを拡大し、欠陥を検出する能力を高め、品質レベルを維持することで、テストの並列化を強化し、コスト削減を図ることを意味します。

一般的に、ウェーハテストやミッションパターンテストでの歩留まりが高いテスト項目、あるいはスキャンテスト時間が長くなる高歩留まりテストは、「シフト・ライト」の理想的な対象となります。これらのテストは、最終テストやシステムレベルテストに移行したり、その中間段階で柔軟に管理したりすることが可能です。例えば、システムレベルテストによって実現される高度な並列処理は、マルチサイトテストならではの経済的メリットをもたらし、品質目標を達成しつつ、さらなるコスト削減を実現します。

テストを前工程または後工程に移す目的は、製造プロセス全体を通じて品質と歩留まりの最適なバランスを実現し、最終的には品質関連コスト全体を最適化することにあります。具体的な戦略としては、以下のものが挙げられます:

- ウェーハプローブ工程における不良品流出率を低減することで、スクラップコストを最小限に抑える

- テストコストを削減するために、最も効率的な方法で量産テストを実施する

- 分析を活用して製造プロセス全体の閉ループ改善を実施し、歩留まりを向上させる。

テラダインのFLEXテストソリューションは、実装工程間でテストを柔軟に移行できるソリューションにより、この「品質コスト」の実現を支援します。EDA、ファブ/パッケージング、データ分析の各分野における強力な業界パートナーシップにより、このプロセスをシームレスに推進します。

データ分析が意思決定の改善を促進する

左シフトか右シフトかの選択に直面した際、テスト戦略の最適化は動的かつ継続的なプロセスであり、その意思決定においてアナリティクスは重要な役割を果たします。テラダインのアナリティクスソリューション「Archimedes」は、チップ製造プロセス全体を通じてテスト戦略を調整するための貴重なデータを提供します。

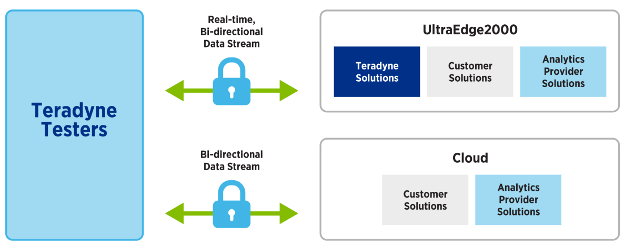

テラダインの「Archimedes」アナリティクス・ソリューションは、データ分析、人工知能、機械学習などの技術をテストソリューションに統合し、テスト時間への影響をほぼゼロに抑えながら、リアルタイムデータの安全なストリームを実現します。これにより、歩留まりの向上、品質の改善、およびテスターのダウンタイムの削減が可能になります。

これは、2.5D/3Dパッケージデバイスに関する有益な知見を確実に得られるよう、標準機能とカスタムソリューションの両方をサポートするオープンな開発環境です。業界トップクラスの分析プロバイダーとの緊密な連携により、高度なデバイスに関する目標を達成できるソリューションをお選びいただけます。

設計からテストへの橋渡し

チプレット技術においては、欠陥の流出を抑制することだけが課題ではなく、歩留まりも考慮する必要があります。歩留まりを向上させるためには、設計からテストまでのギャップを埋めることが、エンジニアリング効率を高めるための鍵となります。 新しいワークフローでは、デバイス開発を加速し、知見を蓄積するために、設計、製造、テストの各エンジニアリングチームがシームレスに連携する必要があります。ATEやSLTテストシステム上でEDAツールやJTAGツールを利用可能にするだけでなく、設計エンジニアとDFTエンジニアがシームレスに連携し、重要な知見を共有してシリコン開発を加速し、学習曲線を短縮できる共通のライブラリやデバッグツールセットを用意することも有効です。

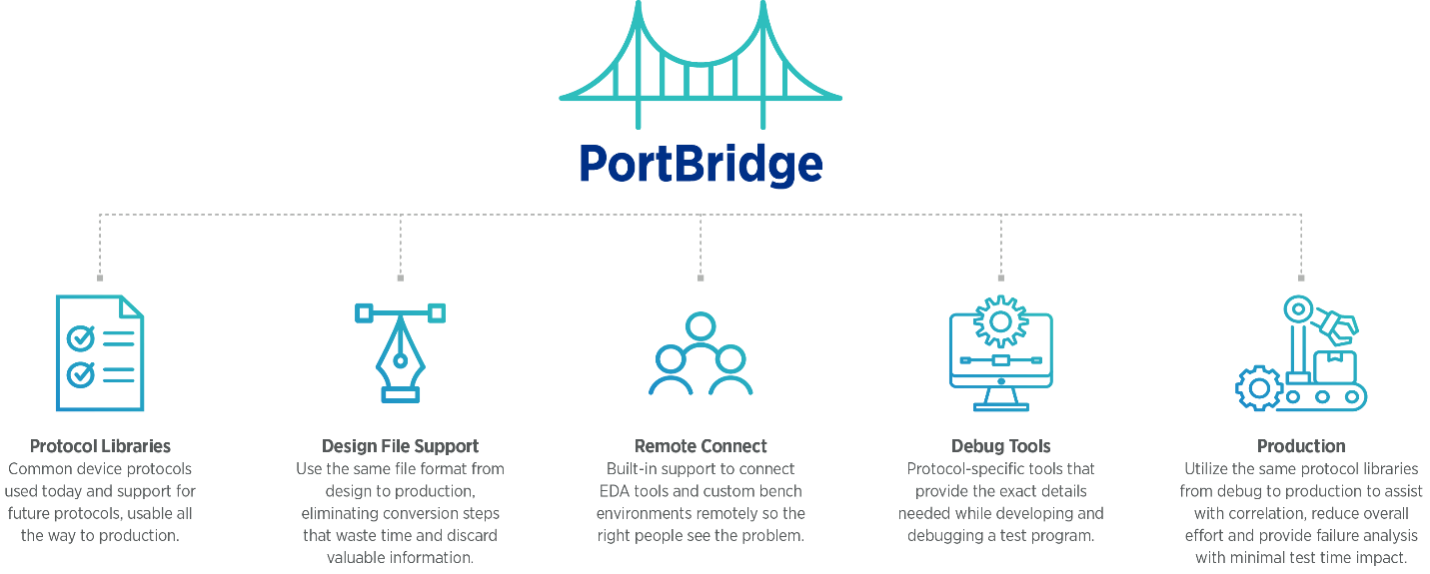

テラダインの「PortBridge」は、設計とテストの間のギャップを埋める汎用ツールセットであり、製造プロセスのどの段階でも導入して、歩留まり向上の機会を特定、実施、検証することができます。具体的には以下の機能が含まれます:

- システムレベルテストにおける不具合のデバッグ

- 最終テスト挿入における不具合の理解

- ウェーハ検査時のテストカバレッジを向上させ、欠陥の見逃しを削減する

- 生産フローの非効率性を明らかにし、デバイスの品質向上、欠陥の低減、および歩留まりの向上を図る

PortBridgeは、Teradyneの UltraFLEXplus およびUltraFLEXテスター に対応し、以下の機能を提供します:

- 現在使用されている一般的なプロトコルや、将来必要となるプロトコルに対応したライブラリ。本番環境での運用までそのまま利用可能です。

- 「Remote Connect」は、EDAツールやカスタムベンチ環境をATEにリモートで接続するための機能を標準搭載しています。これにより、問題解決に最適な担当者が、慣れ親しんだツールや環境を活用して作業を行うことが可能になります。

- 「デザインファイル対応」機能により、SVFなどの標準デザイン形式やカスタム形式を利用できるようになり、時間を浪費し、貴重な情報を失う原因となる変換作業を省くことができます

- テストプログラムの開発およびデバッグ時に必要な正確な詳細情報を把握できるよう、プロトコル固有のツールをすぐに利用可能な状態で提供するホストデバッグツール

- 「プロダクション・イネーブルメント」により、デバッグから本番環境まで同じプロトコルライブラリを使用できるため、相関関係の把握が容易になり、全体的な作業負荷を軽減できるほか、最適なテスト時間で障害分析を行うことが可能になります。

PortBridgeなら、プラットフォームやソフトウェアに最適化されたソリューションにより、デバッグにかかる時間を数ヶ月から数日に短縮できます。

2.5D/3Dパッケージング技術は、次世代のムーアの法則を継続するための道筋を提供しますが、欠陥の迅速な特定と最適化の早期実施こそが、コスト効率に優れた大量生産の鍵となります。テストプロセスを十分に理解し、テストを前工程または後工程にシフトさせることで欠陥の流出率を低減し、製造プロセスにおけるスクラップコストを削減することは、これらのコンポーネントの総製造コストを最小限に抑えるための戦略の一つです。 この柔軟性に、設計およびテストエンジニアリング分野の機能統合を組み合わせることで、最適な品質コストを実現しつつ、不具合の迅速な特定、デバッグ、および排除が可能になります。また、効率向上のために各ステークホルダーがそれぞれの役割を果たす必要がありますが、主要なステークホルダー間、ひいては業界全体での連携こそが、運用効率を最大化するための成功の鍵となります。

最適なテストプロセスの実現を支援するテラダインのソリューションについて、詳しくは弊社までお問い合わせください。

フィッシャー・チャンは、テラダインの半導体テスト部門において、アジア地域の複合SOC事業ユニットのゼネラルマネージャーを務めており、コンピューティング、自動車、ワイヤレス分野における最先端ソリューションの推進に注力しています。フィッシャーは半導体業界で17年以上の経験を有しています。テラダイン入社以前は、アドバンテストおよびコーフーにおいて、アプリケーションエンジニアリング、営業、マーケティングの各部門で要職を歴任しました。フィッシャーは東南大学にて、回路・システム工学および情報工学の理学士号および理学修士号を取得しています。

フィッシャー・チャンは、テラダインの半導体テスト部門において、アジア地域の複合SOC事業ユニットのゼネラルマネージャーを務めており、コンピューティング、自動車、ワイヤレス分野における最先端ソリューションの推進に注力しています。フィッシャーは半導体業界で17年以上の経験を有しています。テラダイン入社以前は、アドバンテストおよびコーフーにおいて、アプリケーションエンジニアリング、営業、マーケティングの各部門で要職を歴任しました。フィッシャーは東南大学にて、回路・システム工学および情報工学の理学士号および理学修士号を取得しています。