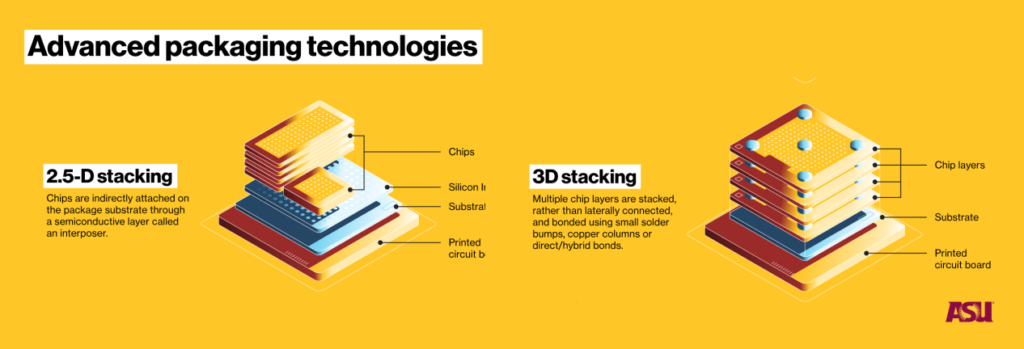

半導体業界がチプレット、2.5D/3Dパッケージング、およびヘテロジニアス統合へとますます移行する中、テスト分野には重大な新たな課題が生じています。テラダインのような業界リーダーは、こうした課題に対応し、革新を起こすために必要な技術を有していますが、業界を円滑に機能させ続けるためには、効果的な連携が必要であり、そのためには標準化が不可欠です。

テストのエコシステムにおいて、効率的な連携を実現し、イノベーションを促進し、テストの効率を向上させるために、標準化が重要となる分野は数多く存在します。大まかに言えば、これらの標準はすべて集積回路(IC)や半導体デバイスのテストおよび通信プロトコルに関連しており、高度なシステムにおける相互運用性、データ転送、および信頼性を可能にしています。

関連する規格には、以下のものがあります:

- PCIe(Peripheral Component Interconnect Express):コンピュータのコンポーネントを接続するための高速通信規格

- MIPI(Mobile Industry Processor Interface):モバイル機器で使用される高速通信規格

- UCIe(Universal Chiplet Interconnect Express):ヘテロジニアスシステムにおいて、チプレットと2.5D/3Dパッケージ間の効率的な相互接続を実現することに重点を置いている。

- IEEE 1838:3D ICの試験に関する規格を定めており、特にシリコン貫通ビア(TSV)を備えたデバイスを対象としている。

- JTAG1、1149.6、およびその派生規格であるJ2C:IC内部の配線をテストおよび診断するためのバウンダリスキャン規格

- SPI(シリアル・ペリフェラル・インターフェース):マイクロコントローラと周辺機器を接続するために使用される一般的な通信プロトコル。

これらの規格は総じて、高度に相互接続されたエコシステムにおいて、半導体デバイスのシームレスな機能性、製造性、および拡張性を保証するものです。テラダインのジョージ・ウルタルテが、重要な規格、それらがテストに与える影響、そして統一されたテスト・エコシステムに向けたテラダインのビジョンについて考察しています。続きをお読みください。

高性能チップをテストするための標準インターフェース

業界標準は、半導体デバイスの機能、性能、信頼性を評価するための一貫した手法を確立することで、効果的な半導体試験の実施において極めて重要な役割を果たしています。これらの標準は、ますます複雑化する半導体設計、高度なパッケージング技術、および異種コンポーネントの統合によって生じる課題への対応を支援します。

まず、GPUやCPUなどの高性能コンピューティング用チップに接続するための標準インターフェースが存在します。これらは、従来のパッケージ構造のものか、チップレットベースのものかを問いません。これらのインターフェースは、PCIeやMIPIなど、通常はシリアル方式です。

これらのシリアルポートは、スキャンテストを通じてデバイスの内部デジタル回路をテストするために使用できます。ここではシリアルインターフェースが使用されますが、チップ内部に組み込まれた「チェーン」に接続することで、よりパラレルな方式に変換され、すべてのトランジスタを同時にテストします。スキャンテストにはテスター側で大量のメモリが必要となるため、業界全体としてメモリ容量の増強が進んでいます。

また、スキャンにはさまざまな種類があり、その一部はシノプシスやシーメンスといったEDA企業が主導しています。テラダインは、こうした企業と早い段階から連携し、各社のEDAツールがこの種のスキャンテストにおいてどのような機能を提供しているかを把握しています。これにより、事前の計画を立てることが可能となり、テストとツールの統合に向けて万全の体制を整えることができます。

シーメンスのような大手企業は、モニターをチップ上に直接搭載することを推進しています。これらは、チップ内の特定のブロックの状態を監視し、演算能力、信頼性、および潜在的な不具合に関する健全性データを提供する、極めて小型の演算デバイスです。標準化されたシリアルインターフェースとオンチップモニターの組み合わせは、現代のチップが持つ極めて高い複雑性に対処するというATEの使命を支える上で極めて重要です。

チプレットに特化した規格についてはどうでしょうか?

新興技術であるチプレットにおいて、おそらく最もよく知られている規格はUCIeであり、これはダイ間またはチプレット間の相互接続に焦点を当てたものです。UCIeはチプレット間でミリメートル単位の短い通信距離しか持たないため、テスト性の課題が生じます。これにより、装置が静電気放電(ESD)に対してより敏感になる可能性があり、この分野ではテラダインが貢献してきました。

3D積層集積回路のテスト・アクセス・アーキテクチャに関する規格であるIEEE 1838を、パッケージング前後のテストに適用すべきである。IEEE 1838は、3D IC向けのDfT(テストを考慮した設計)規格である。DfTは、組み込みコアや3D相互接続を含む可能性のある複数の積層ダイを個別にテストできるアーキテクチャを構築する方法を規定している。

インターポーザーのテストは、主にポイント・トゥ・ポイントの導通検査によって行われます。正常動作が確認済みのインターポーザー(KGI)は、先進的なパッケージにおいて十分な歩留まりを確保するために不可欠です。

パッケージ実装後の組み立て工程において、IEEE P1838のプライマリおよびセカンダリTAPポートを利用することで、ダイ間テストアクセスおよび相互接続の性能整合性を検証することが可能となる。

その他の規格と試験への影響

新たな規格としては、JTAG 1149.1 や 1149.6、SPI、J2C(JTAG to CPU)などが挙げられます。これらはそれぞれ、設計段階および製造段階の両方において、集積回路(IC)の効果的な通信、デバッグ、および検証を確保する上で極めて重要な役割を果たしています。

JTAG 1149.1(IEEE 1149.1規格としても知られる)は、バウンダリスキャン・テストに使用されます。これにより、物理的なテストプローブを使用することなく、PCB上の個々の部品をテストすることが可能になります。この規格は、ICの内部信号にアクセスしてテストする手段を提供し、開回路、短絡、配線不良などの不具合の検出を可能にします。 JTAGは、製造後のチップや基板のテストを可能にし、デバッグや回路動作の検証に不可欠です。

JTAG 1149.6は、1149.1規格を拡張し、現代のICでますます一般的になっている高速差動信号(LVDS、USB、高速シリアルインターフェースなど)のテストをサポートするものです。これにより、これらの高速インターフェースの整合性をテストし、特に従来のバウンダリスキャン技術では信号品質や伝送状態を十分にテストできないシステムにおいて、それらが適切に機能することを保証します。

J2Cは、テスト、デバッグ、およびプログラミングのためにCPUやSoC(システムオンチップ)に直接接続するために使用されるJTAGのバリエーションです。J2Cは、テスト目的でCPUの内部状態、レジスタ、およびメモリへのアクセスを提供します。これは半導体テストにおいて極めて重要であり、特に複雑なプロセッサの開発におけるデバッグや、製造後のCPUやSoCが期待どおりに動作することを検証する際に不可欠です。

半導体テスト環境において、SPIはチップや基板上の組み込みコンポーネントやメモリデバイスとの通信によく使用されるシリアル通信プロトコルです。テスト装置はSPIを介してICと接続し、機能検証、データ転送テスト、およびメモリのプログラミングを行います。

これらの規格は、試験装置と被試験デバイス(DUT)間のアクセス、制御、および通信経路を提供するため、半導体試験において不可欠です。これらは、短絡、開回路、信号整合性の問題などの不具合を特定し、故障検出を可能にします。また、テストパターンの読み書きを通じてデバイスの正常な動作を保証し、設計および製造段階における問題をエンジニアが特定・修正できるよう支援することで、デバッグや検証を促進します。このリアルタイムデータは他の試験システムと共有することができ、試験の効率向上に寄与します。

データ標準化は効率性を向上させる

半導体のテストでは膨大な量のデータが生成されますが、これをデータ分析プラットフォームやその他の下流システムとリアルタイムで共有することで、効率性と歩留まりの面で大きなメリットが得られます。

しかし、企業によってデータ形式が異なり、互換性がない場合があります。SEMIの「Smart Data & AI Initiative」は、ファブ内の各部門間でデータを共有するためのフレームワークを提供することで、この問題に対処しています。

「SEMIの『Smart Data & AI』イニシアティブは、半導体プロセスにおけるデータ分析、機械学習、AI、デジタルツインを活用し、エコシステム全体を通じた連携を可能にします」と、SEMIの『Smart Data & AI』イニシアティブ・グローバルリード兼戦略技術アドバイザーであるプシュカル・アプテ博士は述べた。「半導体デバイスや、その性能、信頼性、総合的な品質をテストするATEシステムの複雑化が進む中、こうした知見を共有することは、イノベーションのペースを加速させる上で極めて重要です。」

このイニシアチブのメンバーとして、テラダインはテストデータ出力の標準化に取り組んでおり、これにより、知的財産の漏洩やベンダーロックインのリスクを伴わずに、連携を促進することを目指しています。同社は、ベンダーに依存しない分析戦略をサポートするオープンな開発環境である「Teradyne Archimedes」分析ソリューションを開発しました。

Archimedesはテストデータへのリアルタイムアクセスを提供し、より効率的な分析と迅速な意思決定を可能にします。Teradyneは標準化されたデータフレームワークをサポートすることで、より協調的で革新的な半導体エコシステムの構築に貢献しています。

標準、連携、およびテストの統合

AI、異種統合、チプレットの時代において、さまざまな規格が、複雑な半導体システムを効率的かつ正確にテストすることを可能にし、高品質な製品が市場に届けられるよう支えています。

半導体業界が進化を続ける中、テラダインは、テストの未来を形作る規格の開発と導入において、常に最前線に立ち続けています。UCIeやIEEE 1838といったチプレット関連の規格から、「Smart Data & AI Initiative」を通じたデータ規格に至るまで、テラダインの貢献は、リアルタイムのテストデータへのアクセスを基盤とした、より効率的で信頼性が高く、協調的な半導体テストプロセスの道を開いています。 今後もテラダインは、次世代の半導体技術に不可欠な規格の策定と推進において、引き続き極めて重要な役割を果たしていきます。

ジョージ・S・ハルタルテ博士は現在、テラダインの半導体テスト部門においてプロダクトマーケティング担当シニアディレクターを務めています。ジョージはこれまで、テラダイン、ラム・リサーチ、ライトポイント、トランスイッチ、ロックウェル・セミコンダクターズにおいて、技術、管理、経営の各分野で様々な役職を歴任してきました。彼はIEEE 802.11 Wi-Fi標準化委員会の投票権を有するメンバーであり、IEEE 802.11ayタスクグループの幹事を務めています。 現在、ジョージ氏はIEEEヘテロジニアス・インテグレーション・ロードマップ(HIR)テスト・ワーキンググループの共同議長を務めるとともに、カリフォルニア大学サンタクルーズ校およびフェニックス大学の客員教授も兼任しています。