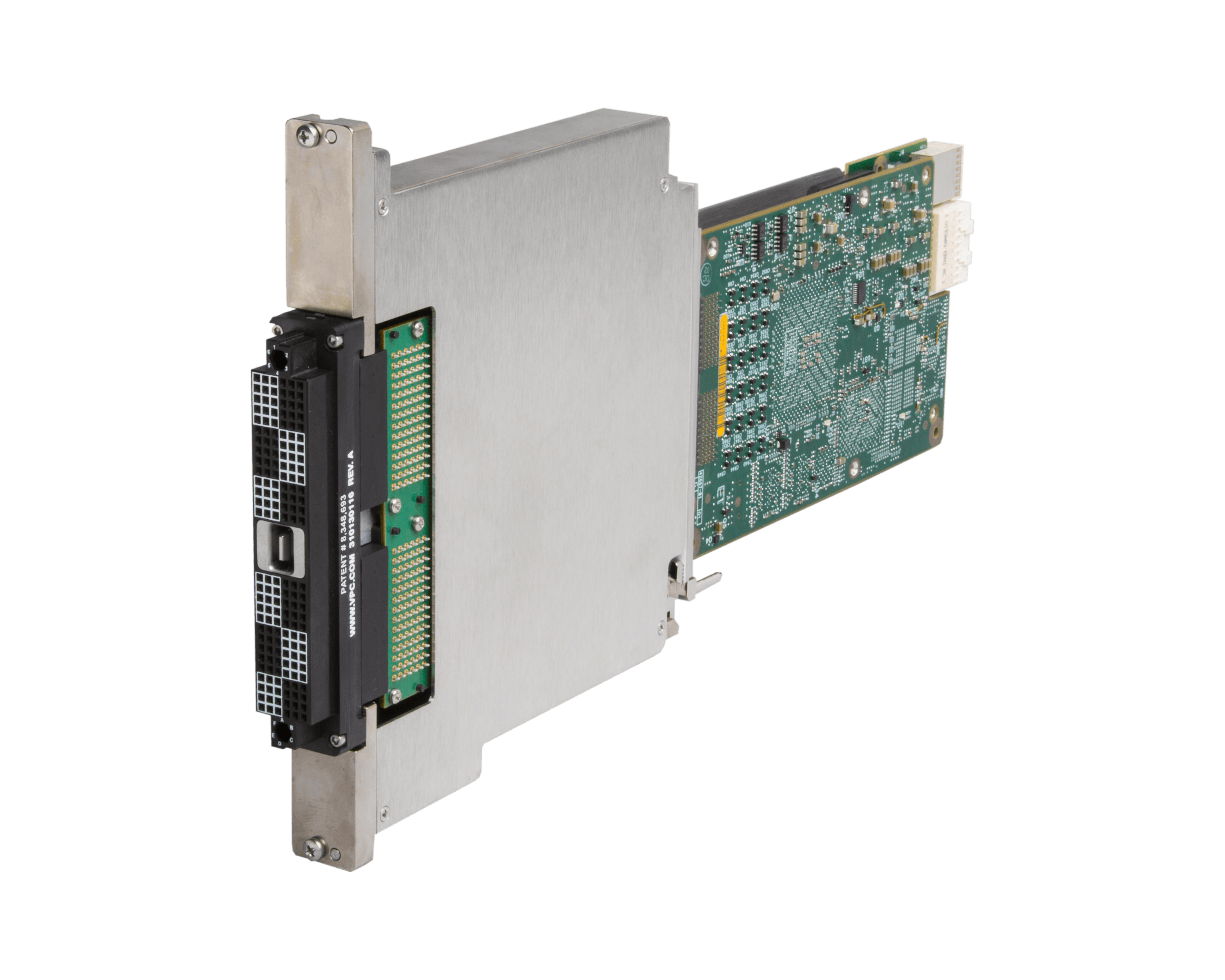

- 統合型計器およびバージニア・パネル・ファンネル・インターフェース

- QuadraPaddleインターフェースモジュールを備えた一体型計測器およびファンネルアセンブリ

- i2 MXケーブルとG20 ITAの両方に対応しています

- 3.3V LVTTLはTTLトレラントで互換性があります

- 最大64本のLVTTL入出力ピン、または32組のLVDS差動ペアに対応

- IEEE 1149.1 バウンダリスキャンの幅広いサポート

- 主要なサードパーティベンダーのランタイムソフトウェアに対応

- 大容量フラッシュの書き込みによる従来の相互接続テスト

- 複数のテスト用アクセスポートと多ピン数の並列I/O

- シリアル・ベクター・フォーマット(SVF)の実行機能(TriFlexソフトウェアに含まれるHSSub )

- Teradyne eDigitalHSSub 、従来の保存パターン(真理値表)テスト機能を提供します(HSSub ソフトウェアに含まれています)

- 柔軟な低レベルHSSub 1 I/Oバス処理

- 大規模なテスト定義FPGAおよびローカルメモリによって実装された、HSSub アーキテクチャのうち、再構成HSSub 1(I/Oバス処理)

- Teradyne、エンドユーザー、およびサードパーティ開発者がサポートするHSSub により、数秒で設定可能

- 必要に応じて、標準的な設計パターンに基づいたFPGAテンプレートコードにより、HSSub の開発が簡素化されます

- HSSub インフラストラクチャ・ソフトウェアのインターフェースにより、Windows Tier 3 またはHSSub 2 計測器からハードウェアにアクセスできます