デバイス・インターフェースソリューション

次世代技術の最適なテストを可能にする

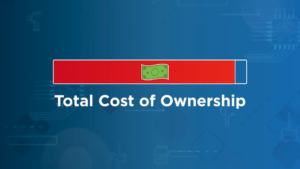

複雑なICには高性能なテスト機能が必要ですが、テラダインのデバイス・インターフェース・ソリューション(DIS)は、その性能をすべて兼ね備えています。 業界をリードする性能と、確かな品質、信頼できるオンタイム・デリバリー(OTD)を組み合わせることで、総所有コスト(TCO)の低減に成功する方程式ができあがります。

Calculate Your Savings

Use the DIS Total Cost of Ownership Calculator to evaluate with your own numbers, how much you can save by using Teradyne Device Interface Solutions.

複合デバイスメーカーがテラダインのDISに注目する理由とは?

DISは複雑なデバイスを理解し、お客様により低い所有コストのソリューションを提供します。 最高のテスト経済性を実現するために、私たちはパフォーマンスを優先しています。 パフォーマンスとは、電力とシグナル・インテグリティを最大化し、並列度を高め、ICの歩留まりを向上させ、テスト(スキャンクロック速度)を速くすることです。 私たちは、初日には欠陥のないハードウェアを提供し、生産期間中はより高いアップタイムを実現する品質を提供します。 DISは、新製品導入(NPI)とリピートオーダーの両方において、信頼性の高いオンタイム・デリバリー(OTD)を約束し、お客様の生産拡大計画や最終顧客の需要に対応しています。 リードタイムの短縮をサポートするため、効率的な開発と製造に注力し、最初のウェハー検証や量産立ち上げをサポートするために、初期段階から要件を満たすようにしています。 複合デバイスメーカーがDISを利用するのは、これらの重要な要素を一貫して実現し、より低い所有コストを達成するためです。

デバイスの複雑さ

セミコンダクタテストにおいては、複雑さの時代が到来しており…そして進化しています。 実際、デバイスの複雑化傾向は、4年ごとに2倍のピン、2倍のパフォーマンスという割合で増加しています。 2×4スケーリングと呼ばれるこの開発では、プローブカードの複雑さが増し、インターフェース・ハードウェアのライフサイクルにおけるシステム開発アプローチの必要性が生じています。 複雑さが増す一方で、デバイスのサイズは大幅に縮小しています。 現在、複合デバイスのサイズとしては、5nmが業界の標準となっています。 しかし、2025年までには、設計者は2-3nmの領域で仕事をするようになるでしょう。 今日のテスト戦略は準備できていますか? インターフェースは、テストインスツルメントと同様に複雑化しています。

インターフェース・ハードウェアの複雑さ

複雑なデバイスでは、独自のピン密度、速度、電力、熱の要件を考慮する必要があります。 DISは、DUT(Device Under Test)サイトの増加やピン数の増加により、ピンエリア密度が上昇し、I/Oや電源をDUTに配線する必要があり、機械的負荷が増加することを認識しています。 複雑なデバイスでは、高速デジタル、ワイヤレス、高電圧などの高性能I/Oへの接続が必要ですが、非常に狭いピン間隔とDUT数で組み合わせると、シグナル・インテグリティの問題が発生する可能性があります。 大電流(>25A)デバイスの電源には、優れた精度と低電圧(<700mV)が要求され、電源レールの数が増加しています。 最後に、弊社は、自己発熱によるDUTの熱エネルギーを除去することがいかに重要かを理解しており、トランジスタ数の増加と狭いDUT間隔の組み合わせにより熱密度が急速に増加する中で、動作温度範囲の拡大をサポートしています。

また、複雑なデバイスの場合、マーケットウィンドウは短くなります。 さらに、クラウド・コンピューティングとストレージのコストは、3年ごとに約50%ずつ下がっています。 AI、RF、PMIC、ハイエンドモバイル、ハイパフォーマンス・コンピューティングのアプリケーションは、多くの分野で評価と最適化が必要な新しい経済性を推進しており、TCOの把握が必要なことは明らかです。

システム開発のライフサイクル

複雑性の管理原則には、統合されたシステム・マインドセットが必要です。 つまり、それぞれの開発フェーズが他のフェーズとコミュニケーションをとるということです。 インターフェースのライフサイクルの各主要フェーズは相互に依存しており、各フェーズにおけるフィードバックの品質がシステム全体の堅牢性に影響を与えます。

システム開発のアプローチには以下が含まれます: インターフェース設計、インターフェース製造、性能検証、診断/QC、保守、サービス、生産業務支援。 このアプローチのゴールは、設計と製造が完全に統合されたソリューションです。 厳密な仕様と品質管理により、不良品を流出させるようなコスト的失敗を避けることができます。 統合された認証、修理、メンテナンス・キャリブレーション、Bin-1バリデーションによって完成します。 設計と製造が統合されたシステムは、複雑さが増すにつれて、効果的に拡張することができます。

総所有コスト

インターフェース・ハードウェアの複雑さは、時間(製造テストの時間と製造リリースのタイミングの両方)と歩留まりに影響を与えます。 TCOモデルは、従来のモデルをベースに、半導体企業のバリューチェーン全体で重要な指標である時間と歩留まりの影響を含むようにしたものです。 半導体の開発ライフサイクルは、テストの観点から大きく4つのフェーズに分けられます: インターフェース・エンジニアリング、テスト・エンジニアリング、ランプ・エンジニアリング、プロダクション・エンジニアリングです。

インターフェース・エンジニアリングのコスト要因は、主にインターフェース・ハードウェアの初期コスト、設計ミスの影響、納期です。 テスト・エンジニアリングの指標には、テスト時間やテスト品質(ゼロエスケープ)などがあります。 ランプ・エンジニアリングには、新製品導入(NPI)ブリングアップ・タイム(市場投入までの時間(TTM))、テストの安定性と再現性などが含まれます。 プロダクション・エンジニアリングでは、ランプアップ・タイム(生産に乗せるまでの時間(TTV))、スループット、歩留まりに注目します。 これらの重要なパフォーマンス指標をすべてモニタリングすることで、パフォーマンス、品質、納期を改善し、所有コストを削減することができます。

コモディティ・ソリューション・アプローチ

インターフェース開発の車輪の中で独立したベンダーに引き渡すというプロセスは、レガシー技術ではよく知られていることですが、複雑なデバイスでは単純に実行不可能なことです。 コモディティ・ソリューション・アプローチとも呼ばれるこのアプローチでは、管理されずに検出された欠陥が後工程に引き継がれ、異なるベンダーがプロセスやツールを適応させて補うことができないため、所有コストがかさむことになります。 複雑なデバイスの場合、コモディティ・アプローチの数学は文字通り破綻します。故障検出テストの結果が悪いと一発合格率が非常に低くなり、その結果、製品化の遅れや市場投入の遅れが生じます。 実際、コモディティ・アプローチでは、時間と歩留まりという隠れたコストが、複雑なデバイスではプローブカードのコストの2~3倍になることもあります。 プローブカードがオンタイムで、欠陥なく、完全な性能を発揮すれば、初期費用よりも大きなTCO削減を実現できます。

DISの特徴は、性能、品質、納期を最大限に高めることに注力することでお客様をサポートし、その結果、製品の立ち上げの遅れを防ぐという時間的なメリットと、デバイスの制限や仕様の低性能化を防ぐという歩留まり的なメリットの両方を得ることができる、ということです。 複雑なデバイスのテストを効率的に行うことでTCOを削減できるため、デバイスメーカーは高複雑度のインターフェース・ハードウェアのニーズに対してDISを選択します。

DISは、ウェハーから最終テストまでのソリューションを提供します

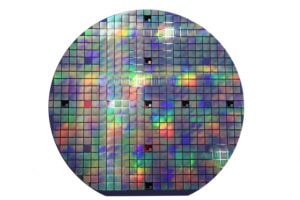

パッケージされた半導体デバイスに含まれるダイは、ウェハーの状態でプローブテストを行い、パッケージ後にファイナルテストを行います。 これらの異なるテスト挿入により、異なるタイプのデバイス・インターフェース・ボードが必要となります: パッケージング前のウェハーにタッチダウンするプローブヘッドと針が一体となったプローブカード(PC)と、パッケージングされたICの形状やサイズに合わせたソケットを搭載し、パッケージングされたデバイス・ハンドラと一体となった最終テスト(FT)ボードです。 DISは、これらのボードやプローバー・インターフェース・ボード(PIB)の設計、製造、組み立ての専門知識を提供します。

DISは、ウェハーテストにおいて、プローブ針との界面が極めて平坦であること、多ピンおよび多サイトのデバイスに対応できること、テスタ信号の性能を発揮できること、ダイの微細なピンピッチ要求に対応できることなどの、テストセルの要求を満たすDIBを製造する専門技術を提供します。

最終テストでは、インターフェースボードは、現在および将来のテストアプリケーションの多ピン、多サイト、シグナル・インテグリティの要件を満たしながら、デバイスをコンタクタに挿入する際に発生する高い挿入力に耐える必要があります。

弊社のハードウェア研究開発センターは、米国のインスツルメント開発チームと同じ場所にあります。この強力なコンビネーションにより、DISはパワー・インテグリティとシグナル・インテグリティを完全に最適化するための優れた電気設計能力を提供することができます。これは簡単に言えば、お客様の新しいデバイスの製造テストにおける、最高のパフォーマンスを達成するための比類ない電気設計を意味します。

より複雑なデバイスを、品質に妥協することなく、より早く市場に投入することが必要であることを、弊社は理解しています。 そのため、DISは非常に複雑なインターフェースを、クラス最高の一発合格品質と安定した納期で提供しています。 顧客の信頼を得て、デバイスを予定通りに生産し、稼働させることができるのです。 また、DISは、インストールにかかる時間を最小限に抑え、納入したインターフェース・ハードウェアのファーストパス品質を最大限に高めるBin 1サービスや、DIBの状態を監視し、検出された不具合に関する診断情報を提供し、高価なプローブヘッドの製造寿命を最大限に延ばす生産ツールも提供しています。

テラダインの設計・製造システム(TDMS)

テラダインは、デバイス製造におけるサイクルタイムの短縮と歩留まりの向上の重要性を理解しており、DISが製造と信頼性のための設計に重点を置いているのはそのためです。 高いファーストパス歩留まりを実現し、予測可能な納品・設置スケジュールを計画することで、ICの立ち上げや大量生産の立ち上げをサポートします。

DISは高度な設計テクノロジーを駆使し、より短いリードタイムで理想の設計に近づけることができます。 弊社は、先進のSiP(System in Package)設計ツールの統合、自動化されたフルボード・シミュレーション機能、設計と製造の検証を強化するための広範囲なCADツールの自動化を提供します。 DISは、これらの独自技術に加え、製造技術や設計ルールをサプライチェーン・パートナーと密接に共同開発することでボードのファーストパス歩留まりを90%以上確保することに成功しました。

DISは、お客様のテスタの効率を最大限に高めるため、最終テストやウェハープローブのアプリケーションで可能な限り多くのサイト数を実現できるよう、継続的に努力しています。 現在、DISでは、デバイスピンピッチ60μmまでのインターフェース・ボードの設計および製造が可能です。 弊社は、DISがお客様のデバイス・インターフェース・ハードウェアのパートナーなることで、お客様の生産現場が最高の効率で稼働することを確信しています。

新しいハードウェア設計のためのテストや診断についてはどうでしょうか? テラダインはテストのリーダーであり、それが私たちの得意とするところです。 オンテスタDIB-Diagnosticsは、短絡ソケット/ウェハーのコンタクトポイントの有無にかかわらず、すべての新しいインターフェース・ボードに対して高い故障検出率を提供することが可能です。 生産フローに統合されたこれらの診断ツールの拡張として、デバイス・インターフェース・ボードの「健全性」を継続的に監視する機能があります。これにより、損傷または欠陥のあるコンポーネントを早期に検出および診断し、品質が不明なハードウェア性能で生産テストを実行することを回避することができ、下流の性能と品質に影響を及ぼす歩留まり低下やテスト漏れのリスクを除外できます。

DISは、テスタ信号をデバイスピンのファインピッチ要件に変換することを可能にする多層有機(MLO)空間変換技術の設計、シミュレーション、および統合の実績があります。 この独自テクノロジーの採用により、TDE(Touch Down Efficiency)に優れた高サイト数のウェハープローブカードを実現しました。

DISがあなたのビジネスに貢献できること

DISは、インターフェース設計の専門家リソースを提供し、インターフェースのニーズに対して「ターンキー」ソリューションを提供します。これにより、お客様のエンジニアリングチームはテスト開発に専念し、テラダインのテスト・プラットフォームの能力をフルに活用することができます。

弊社は、250人以上のグローバルなサポート要員を擁し、新しいデバイス導入のためのローカルデザインを提供する信頼できるパートナーです。 テラダインの経験豊富なDIS設計により、お客様は量産準備のためのハードウェアリリース・スケジュールを予測することができます。

デバイス・インターフェース・ボード(DIB)の設計および製造において、性能、品質、スケジュール、総テストコストの最適化を目指すのであれば、テラダインのデバイス・インターフェース・ソリューション(DIS)が最適な選択肢になります。