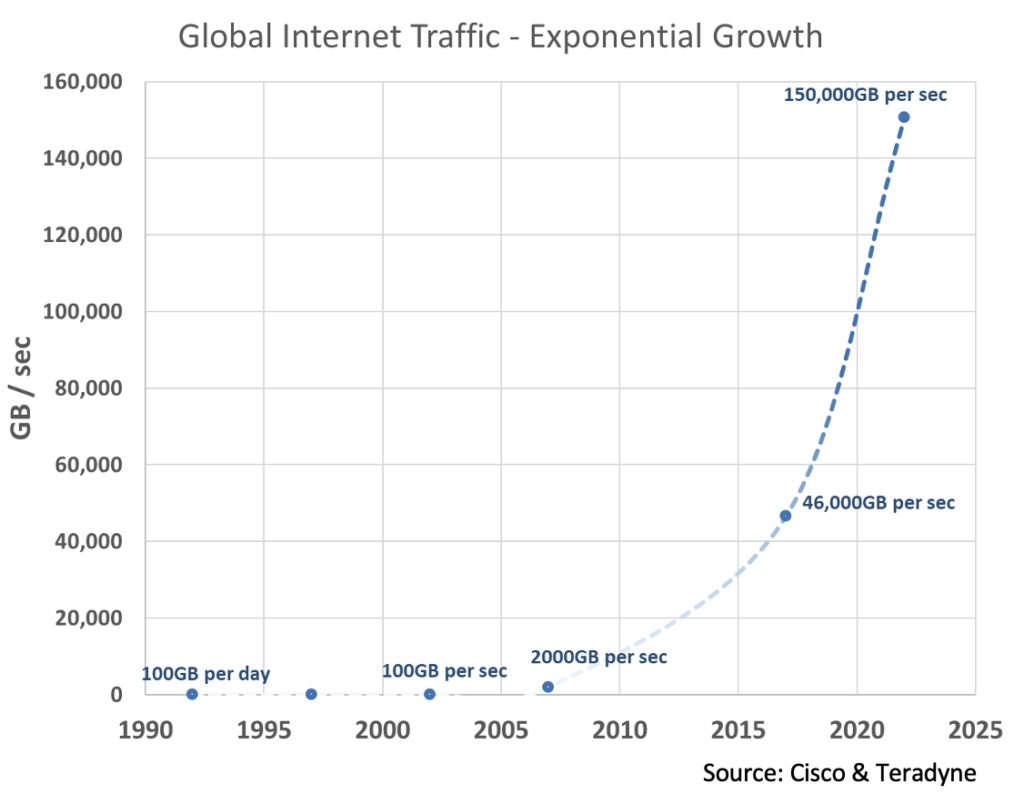

世界のインターネットトラフィックは指数関数的に増加しており、その勢いは衰えることを知らず、この需要がセミコンダクタ業界の進化を促しています。 より多くのデータを取得するためには、データを取得するためのセンサ、データを移動させるためのネットワーク、ストレージ、そしてデータを分析するための処理能力が必要です。 データの需要が高まるにつれ、基礎となる技術は、現在のニーズを満たすだけでなく、将来のアプリケーションに対応するために進歩しなければなりません。

新技術が複雑なデジタルデバイスのイノベーションを促進する

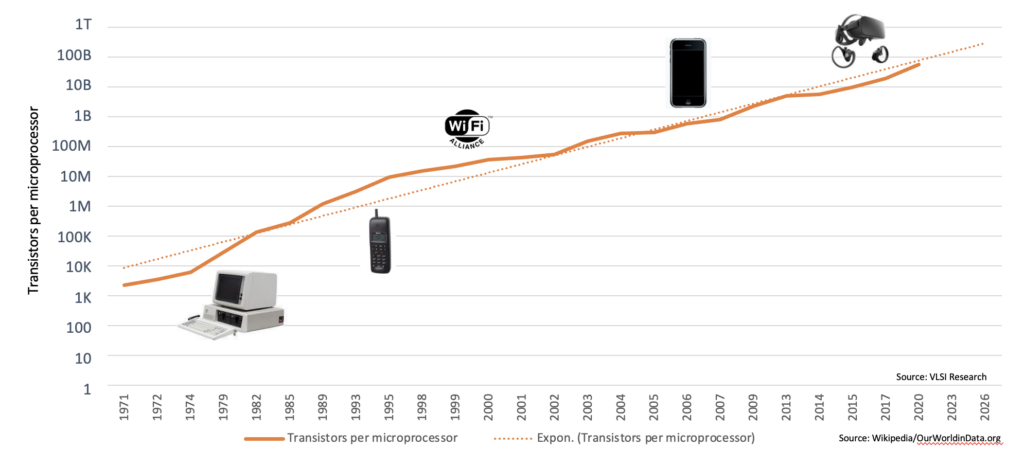

マイクロプロセッサー1台あたりのトランジスタ数の歴史的な増加を見ると、デバイスの複雑さに応じた処理需要のペースも、この50年間に指数関数的な成長経路を続けてきたことがわかります。 より高い処理能力を要求する新しいアプリケーションがこのトレンドの主要な推進力であり、拡張現実のようなアプリケーションのある未来では、性能に対する要求がさらに高まるでしょう。 先端ノードに搭載されるデバイスが増え、これらのチップに対する需要が高まる中、先端セミコンダクタファブへの投資は過去1年間でほぼ倍増しており、1億米ドル以上という新たな水準に達しています。 生産量の増加により、高品質の自動テスト装置(ATE)の需要が高まり、チップの複雑化により、テストに新たな課題が発生しています。

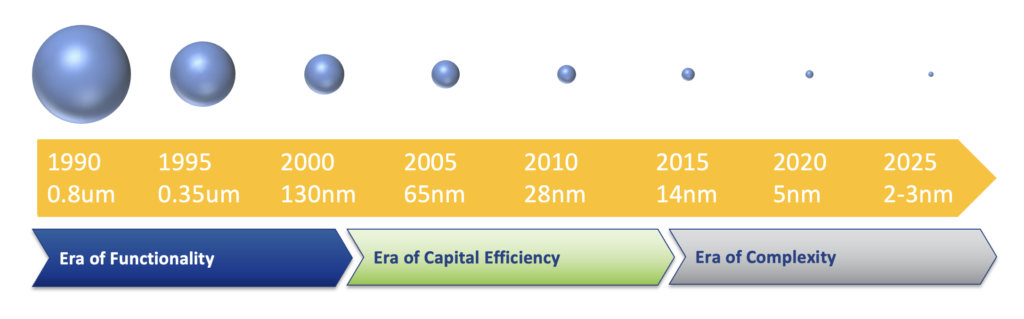

セミコンダクタテストの変遷を振り返ると、1990年代は機能テストをするということが課題でした。 その次の時代は、テスト時間を短縮し、並列度を高めた高スループットのテスト装置によるコストダウンに重点を置いた時代です。 そして、ここ数年は、(2011年にIntelが22nmのFinFETに移行したことを皮切りに)セミコンダクタの製造プロセスやパッケージングがますます複雑化していることが特徴です。 弊社は、これが少なくとも今後10年に渡って、テストに影響を与える主要なドライバになると考えています。.

セミコンダクタ・デバイスの製造における最新のブレークスルーとして、2次元構造から、より複雑な3次元構造へと進化したGAA(Gate-All-Around)FETトランジスタが挙げられます。 テストとは製造上の欠陥を見つけることですから、このような新しい非常に微細なデバイス構造では、より多くの種類の微妙な欠陥を見つける必要があり、テストの複雑さが増しています。 トランジスタはますます小型化し、1つのダイに多くのトランジスタが搭載されるため、スイッチング電流が増加しています。

それについては、また後ほどご説明しますが、まず、トランジスタの数が増えれば増えるほど、メモリの深さが増し、新しいデジタルテスト技術が生まれ、新しいデジタル・インスツルメントが必要になることを説明します。 しかし、これは主要なベンダーがすぐに対応することなので、別のレベルの課題に目を向けてみましょう。

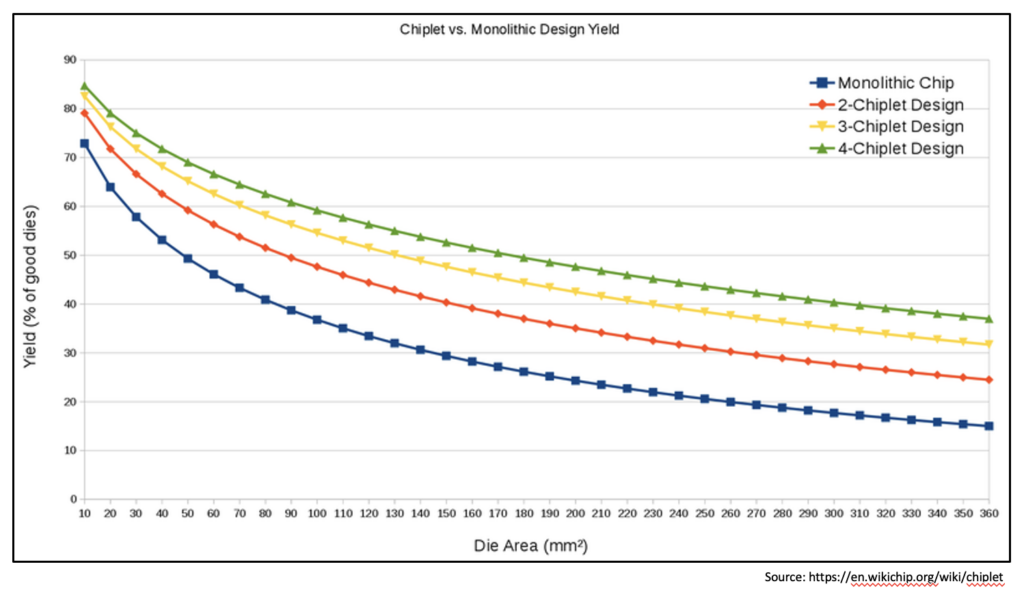

さらに興味深い課題は、ダイのトランジスタ数がますます増えていく中で、いかにして管理可能な歩留まりを確保するかということです。 チップレットは、複数のダイを集積することで、単一のモノリシックなダイの歩留まりよりも高い歩留まりを実現することができると言われていますが、これはテストの課題に影響します。 これらの影響は大きく4つに分類されます:

- 品質

-

- 検証が可能なように設計されたIPブロックでのテストは可能ですが、単体で製造された状態ではテスト不可能なため、追加のダイエリアが必要になる場合があります

- 回避した悪いダイのコストと、ダメになったアセンブリのコストとのバランス

-

- 相互運用性: インターフェイス/インターオペラビリティ・テストのための効率的なテストセットアップを可能にする既存のテスト標準の拡張、およびコスト削減のためのテスト標準の業界採用

- 高速インターフェース: ダイのループバックと、既知の良品ダイをサポートするための十分なウェハーテスト、およびコスト上の理由から限られたドライバ強度でバンプとドライバをテストする必要性

- 高速インターコネクト: テスタのデジタルピンに接続される1/2メートルのインターフェースではなく、基板上の数ミリの銅を駆動することを目的とした、ダイ上の高速インターコネクトとドライバーの管理

スイッチング電流増加の話に戻ると、先進的なプロセスノードの採用によるあまり目立たない影響として、デバイスのテスタ用電源への影響があります。 トランジスタをオン・オフする行為は、本当に小さなコンデンサを充電するようなもので、小さな充電電流しか発生しません。 しかし、100億、200億、500億とトランジスタを増やすと、瞬間的に大量の電流が流れます。 瞬間的に2000Aもの電流を流すデバイスがありますが、プロセスノードが進むと動作電圧は低下します。 この電圧の低下と同時に大電流のスイッチングを行うことは、高度なデジタルデバイスのテストにおける最大の課題の一つであり、デジタルテストにおける最も困難な課題が実際にはアナログの問題であるという、物議をかもす結論に至ります。

従来の電源で広帯域のインターフェースを構築するには、共振周波数に注意してコンデンサのマッチングを行い、緻密なネットワークを構築する必要があります。 テストエンジニアにとって代替となる唯一の真のソリューションは、労力を軽減し、アプリケーションのハードウェアを初めて動作させるダイナミックパワーサプライです。デジタルテストにおいて、本当はアナログの最適解を持つことが重要です。

3Dデバイス構造によるシステムレベルテストの必要性

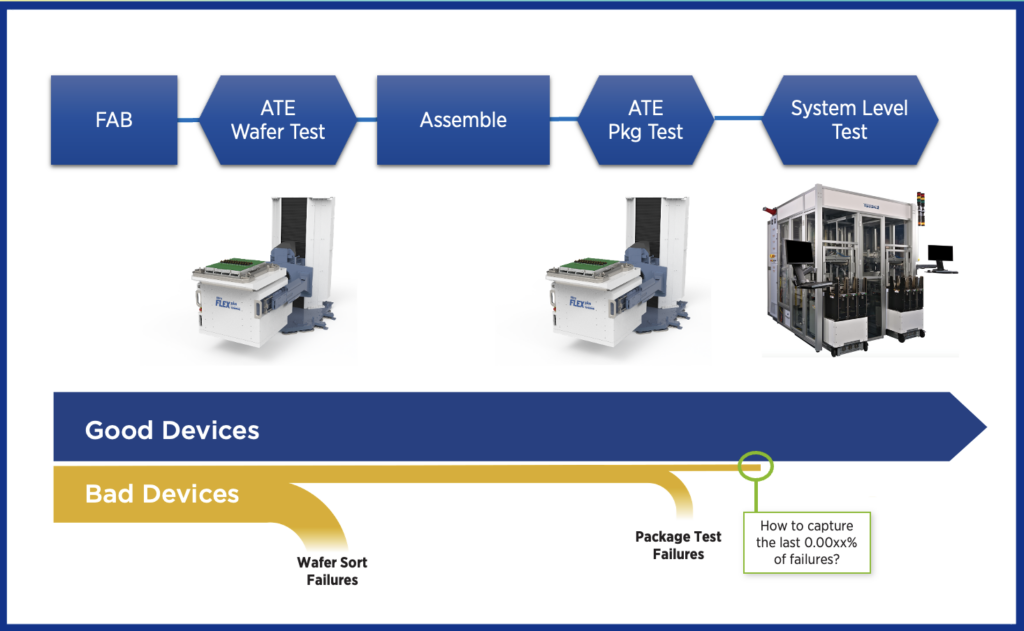

このような複雑な3Dデバイスの構造は、複数の新しい欠陥モードを生み出し、これらの欠陥モードは従来のテスト方法では見つけることが非常に困難であるという事実に目を向けましょう。 不具合はミッションモードのテストでしか現れないこともあり、高度なデジタルデバイスではSLT(System Level Test) 機器の重要性が増しています。

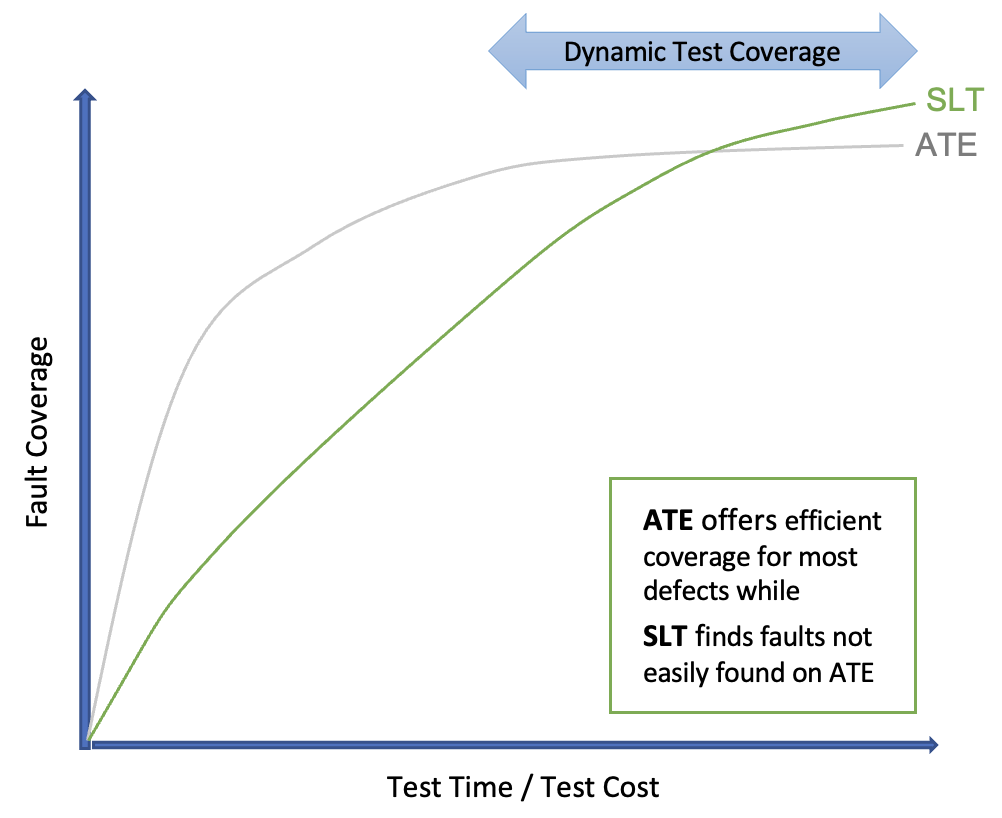

システムレベルテスト は、従来のATEに代わるものではなく、また追加のテストインサーションでもありません。 ATEでの故障検出率は、ある時点までは高速で効率的ですが、それ以降はより微妙な欠陥を見つけるのにかなり時間がかかるようになります。一方、SLTは、最初は時間に対してより直線的な故障検出率ですが、より繊細な欠陥の一部はATEよりも短時間で発見することができます。今後は、ATEとSLTの間でテストカバレッジの最適化が行われるでしょう。 システムレベルテストのユースケースと新たなトレンドを紹介する、弊社の最新のシステムレベルテストの「3 for 3」ショートビデオ が公開されました。

エンジニアリングの効率化で生産性を向上させる

こうした先端デジタルデバイスのテストにおける技術的なハードルを論じるだけでなく、これが本当にセミコンダクタ業界が直面する最大の課題なのか、自問自答してみる必要があるのではないでしょうか。 リチウムやセシウムなどのレアアース資源の限界という現実に直面していることは周知の事実ですが、歴史的に見れば、材料不足を補うためには、代替技術が開発されてきました。 しかし、この業界におけるもうひとつの希少資源であるエンジニアについて考えてみましょう。 業界が指数関数的に成長し、質の高いエンジニアが不足する中、人的資本が業界の成長性に与える影響を最小限に抑えるための戦略を検討することが不可欠です。

採掘して生産量を増やすという、現在のレアアースのようなアプローチも考えられます。 教育機関に生産量を増やすよう求めることもできますし、実際そうしていますが、時間がかかります。 おそらく、私たちが許容できる以上の時間がかかるでしょう。

人工知能もトレンドトピックの一つです。 比較的短期間で長い道のりを歩んできたAIは、より標準的で反復的な作業の一部を自動化することで、コード生成においてエンジニアを支援する日が来るかもしれませんが、近い将来に、AIがエンジニアに完全に置き換わることはないでしょう。

しかし、既存のエンジニアの作業をより効率的にし、生産性を高めることは可能です。 今日のテストエンジニアは、設計から大量生産に至るまでにかかる時間を短縮し、スループットと歩留まりを最大化するというプレッシャーに常にさらされています。 このプロセスには複雑さがつきものなので、この複雑さを最小限に抑えるソリューションを選択することで、生産性を大幅に向上させることができます。 テラダインの製品は、このことを念頭に置いて設計されており、市場投入までの時間を短縮し、歩留まりを最大化する革新的なソリューションが含まれています。

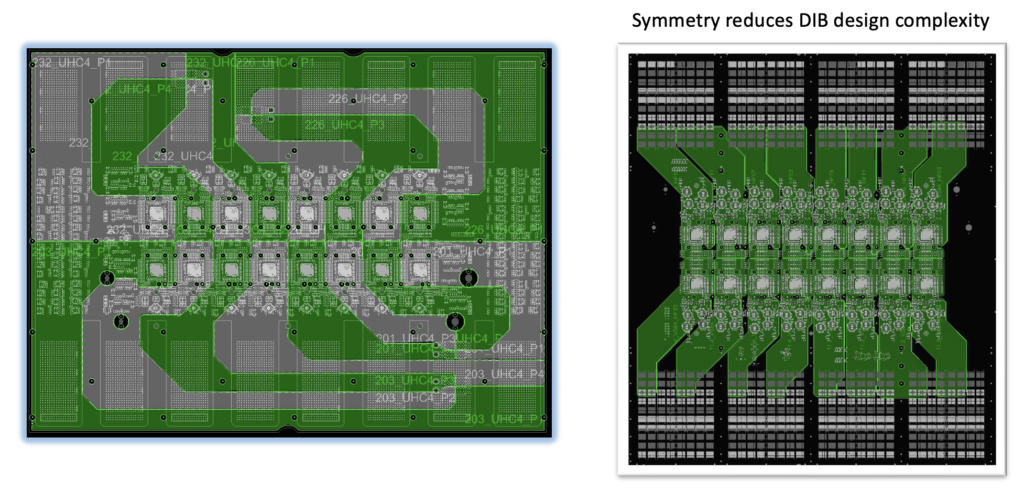

まずは、テストエンジニアの仕事の複雑さを軽減することから始めるとよいでしょう。 もし、各サイトが同じ対称的なデザインを持つことができ、マルチサイトのインターフェースボードが不要になり、最終的にDIBのデザインの複雑さを減らすことができる、優れたデザインのテスタがあったらどうでしょうか。 つまり、設計の手間を減らし、サイト間の相関性を大幅に向上させ、テストエンジニアがテストリストとテスト対象デバイスに集中できるよう、基本的な設計を簡素化することができるのです。

ラダインのUltraFLExplusのBroadsideアプリケーション・インターフェースは、まさにこれを実現しており、DIB回路用の大きなPCBエリアを(PCBの側面に押し出すのではなく)インスツルメント接続とDUTの間に配置することで、サイト間のコピー/ペースト配置と結果としてのレイアウト一貫性を実現しています。 このシンプルさにより、テストエンジニアはDIBの設計時間を節約できますが、さらに重要なことは、マルチサイトでの問題でデバッグ時間が長くなるリスク、あるいはサイト間の設計上の問題でDIBを再作成しなければならないリスクを回避できることです。 Broadsideインターフェースは、マルチサイト性能に対応しながら相関性を高めるため、生産準備の整ったテストプログラムを作成するためのエンジニアリングの労力を20%以上削減し、テストセルの数を15%~50%削減することで製造生産性を向上させます。 アーキテクチャをシンプルにすることで、エンジニアの生産性を向上させることができます。

データもまた、工場の生産性を向上させるために活用できる分野です。 場合によっては、テストフローに沿った低遅延で高速な意思決定が必要で、テスタと緊密に統合されたローカルソリューションが必要になります。 その他のデータのファクタリングについては、クラウドや工場のMESシステムへ行く必要があります。 このデータは、データ分析から決定されたアクションが製造プロセスの他の部分に影響を与えることができるように、お客様のソフトウェアシステム上で動作させることが望ましいものです。 エッジアナリティクスもクラウドアナリティクスも、効率を上げるために重要な役割を担っています。

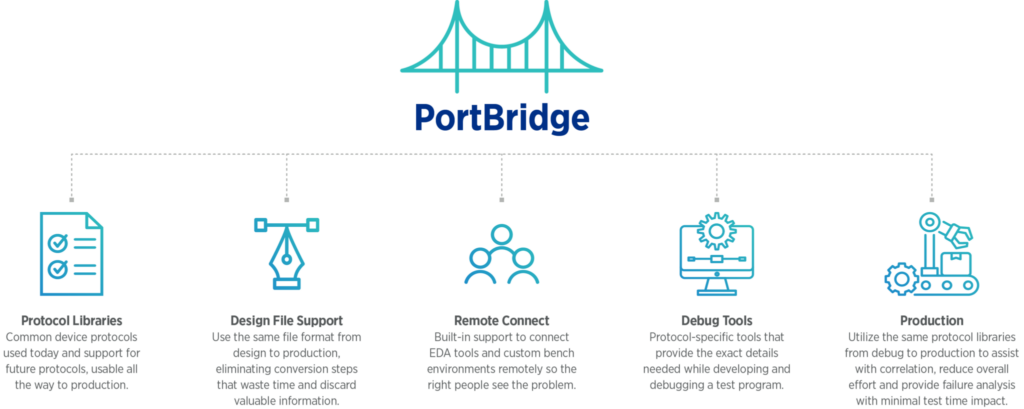

また、エンジニアの効率化の例として、非効率が忍び寄る場所を特定することが挙げられます。 設計の世界とテストの世界では言語が異なり、それぞれの領域のエンジニアは、相手が理解できないような話し方をします。 多くの問題において、テストからの情報を設計チームに戻し、レビューとテストのベクトルの修正を経てテスタに戻す必要があります。 このデバッグループは、何時間も、何日もかかることもあります。テラダインのTeradyne’s PortBridgeのように、これらの世界をつなぐブリッジがあれば、設計エンジニアやベンチエンジニアがATEと直接通信してデバッグしたり、テストエンジニアがフラットパターンの不具合を理解し診断したりできるようになり、情報の流れを合理化することができます。 数週間、数カ月かかっていたプロジェクトが数日に短縮され、大幅な工数削減が可能になります。

アドバンストデジタルは、新たな技術的課題を生み出し、セミコンダクタ業界の成長を制限しないためにこれらに対処する必要があります。 要求や需要に応えるために、技術は常に進化します。 このようなトレンドは、これまでにもいくつか紹介してきましたが、最も効果的なソリューションの中には、エンジニアの生産性を高めるツールを提供するものがあります。 エンジニアは需要の高い希少な資源であり、彼らの生産性を高める先進的なツールや機能を提供することが、飛躍的な成長を実現し続けるための重要な鍵となります。

先進的なプロセスノードに対応したテラダインのテストソリューションの詳細について、弊社までお問い合わせください 。

Regan Millsは、テラダインのマーケティング担当副社長であり、セミコンダクタテスト部門のSOCビジネスユニットのジェネラルマネージャーを務めています。 テラダイン入社以前は、Automation Engineering IncorporatedとArctic Sand Technologiesで管理職を歴任しました。 マサチューセッツ工科大学で電気工学とコンピュータサイエンスの理学士号を、ボストン大学で電気工学、制御システム、デジタル信号処理、アナログ設計の理学修士号を取得しています。