Analog Test

Analog Test Instruments

Analog test building blocks for high performance ATE.

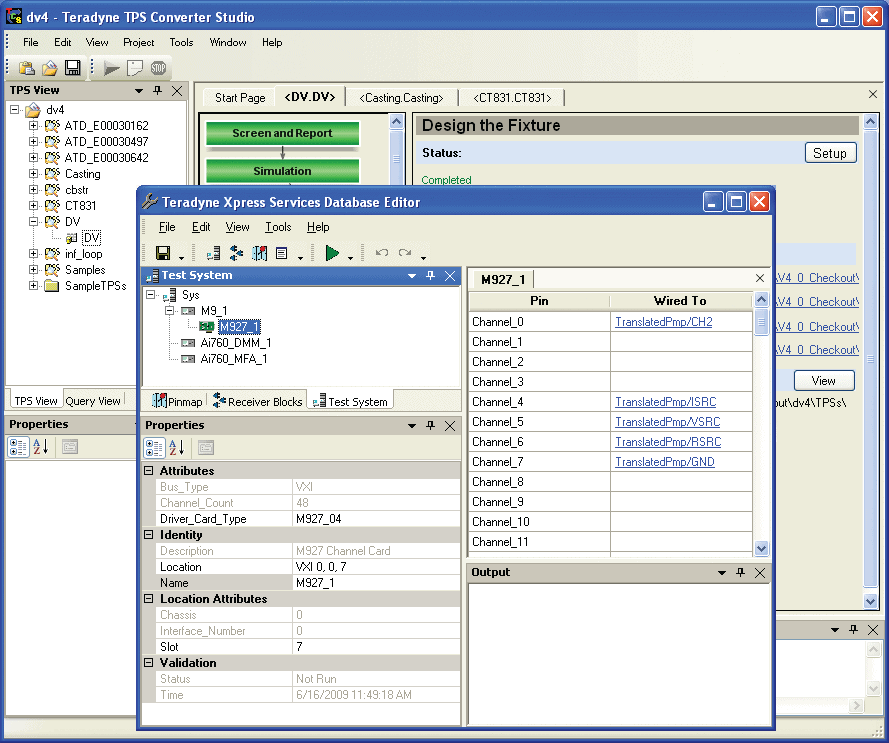

Teradyne offers two families of analog test instruments

- VXI-based Core System Instruments (CSi)

- ZT-Series™ PXI/LXI instruments.

Both families meet today’s demanding test requirements as well as bringing improved test capability to legacy ATE systems.

Older analog instruments found in production and depot test systems used in defense and aerospace applications often result in slow throughput, inadequate test coverage, and spotty fault diagnosis of Line Replaceable Units (LRU)—especially newer units with more stringent performance specs.

Teradyne offers two families of analog test instruments

- VXI-based Core System Instruments (CSi)

- ZT-Series PXI/LXI instruments.

Both families meet today’s demanding test requirements as well as bringing improved test capability to legacy ATE systems.

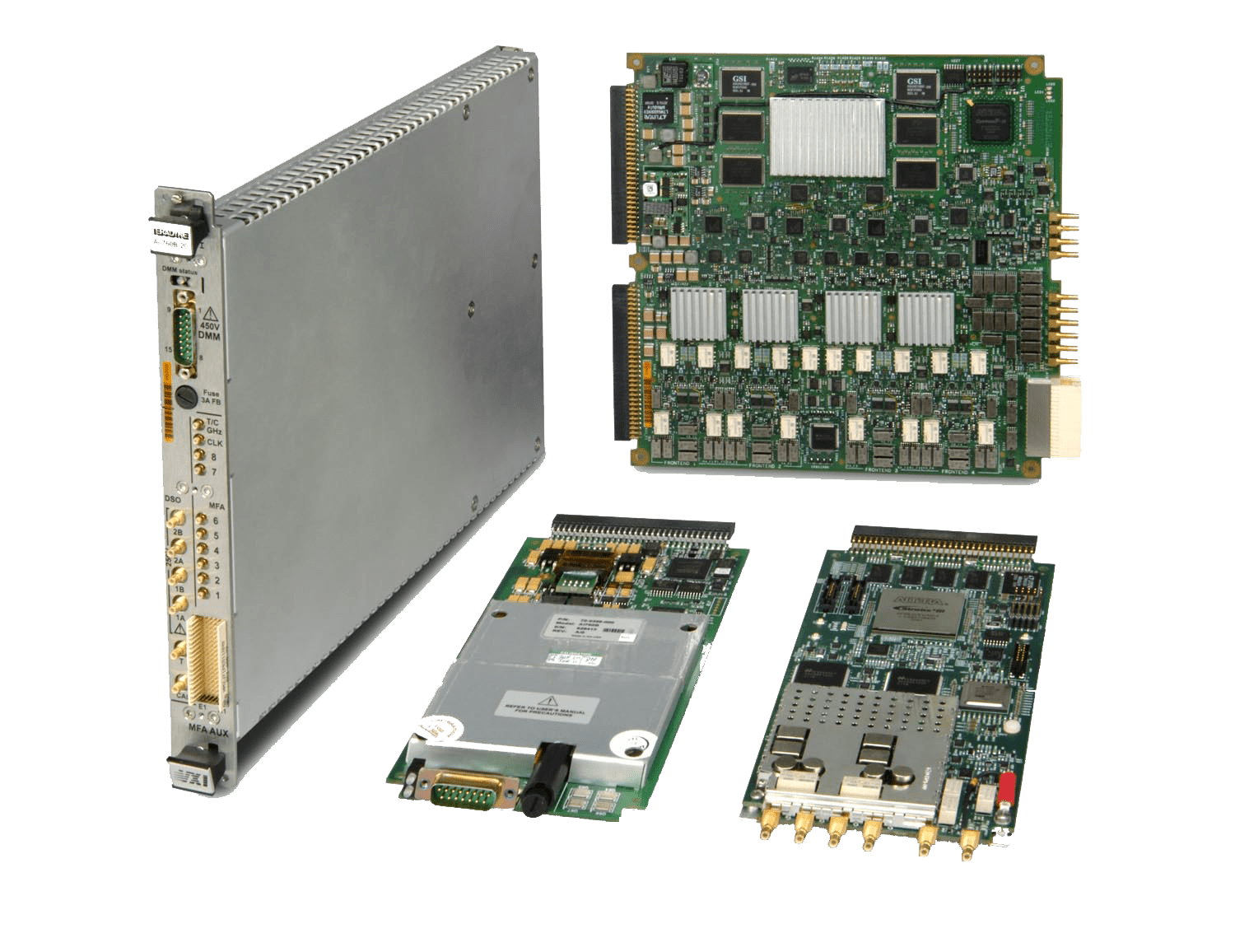

CSi family instruments include Digital Sampling Oscilloscope (DSO), DMM, and Multi-Function Analog (MFA) capabilities that are ideal for both new and existing ATE systems. Several CSi instruments feature multi-channel parallel synchronized capabilities that speed test throughput.

The compact PXI- or LXI-based ZT-Series DSO and Arbitrary Waveform Generator (AWFG) instruments are perfect for new ATE systems requiring a smaller footprint.

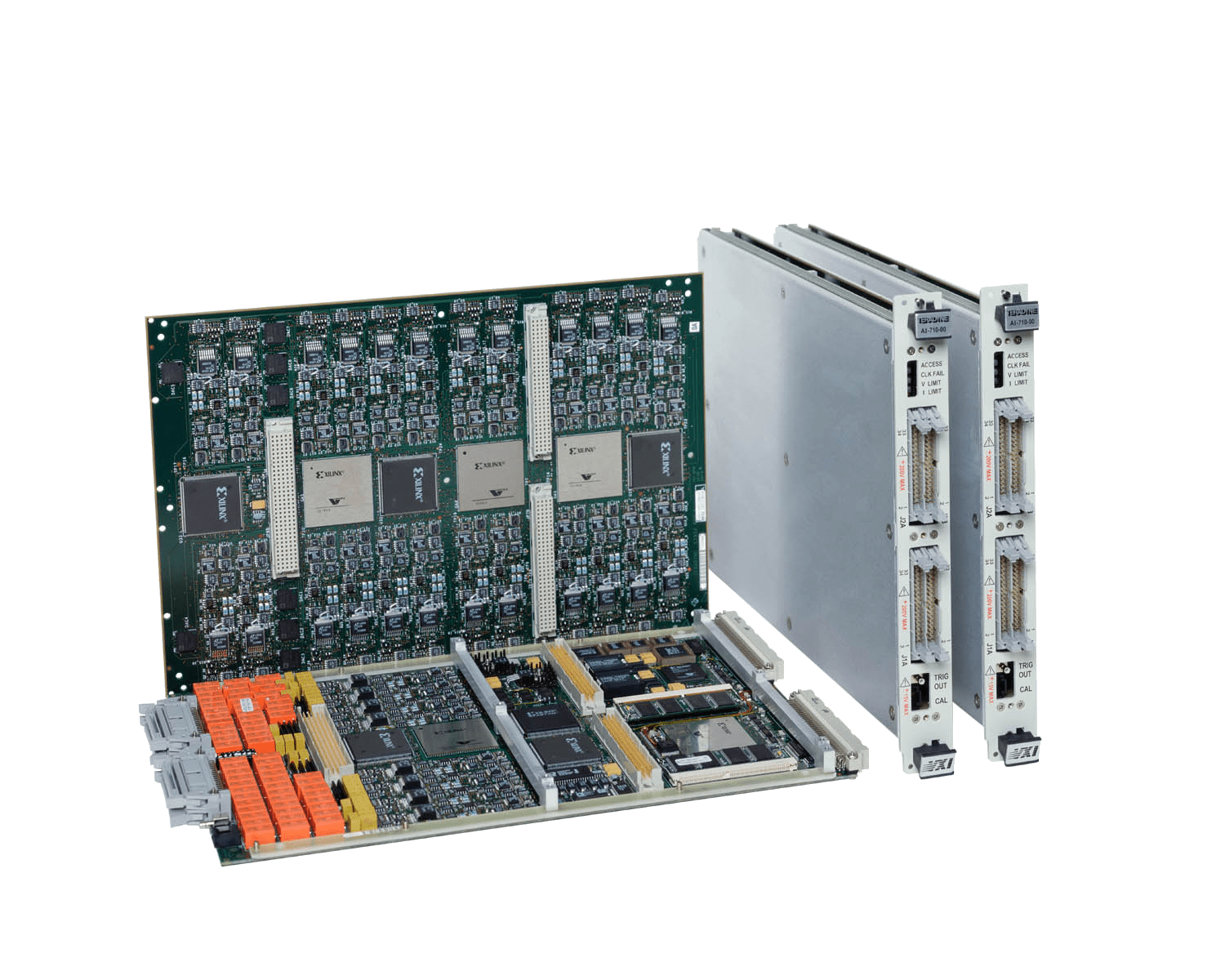

Ai-710

VXI analog test instrument with advanced parallel test capability speeds test throughput.

Ai-762

Standards-based VXI test instrument combines legacy functionality with advanced parallel test capability.

ZT-Series

High-Performance Digital Storage Scopes, Digitizers, Waveform Generators. Modular test instruments for straightforward integration into test systems.

Advantages

Tester-per-pin architecture available on several CSi instruments.

Simplifies Interface Test Adapter design by combining full stimulus/ measurement capability on every CSi analog channel.

Superior test performance across a wide range of specifications.

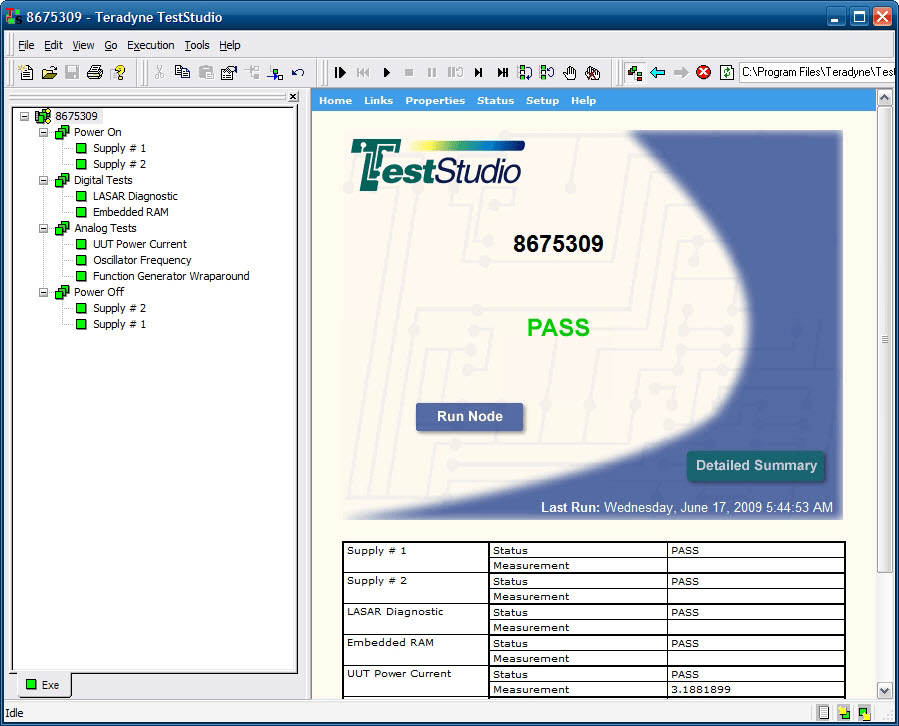

Both families provide high throughput tests and parallel stimulus/measurement of complex systems such as mixed signal Line Replaceable Units (LRU).

High functional density form factors.

Both VXI and PXIe form factors increase channel density while reducing overall test system footprint—and cost.

COTS architecture.

Delivers stimulus and measurement flexibility and high reliability together with lower acquisition cost, resulting in lower life cycle cost.

Worldwide support.

Available support services include 24-hour repair-and-return of defective parts, hotline telephone support and comprehensive training and documentation.

Applications

High performance analog instruments for ATE and legacy test systems.

The optimum test and measurement solution for new mixed signal ATE systems that require high performance and/or multiple channel stimulus measurement functionality in high density, compact packages.

Replace older, slower discrete (rack mount) test and measurement instruments with high-density, advanced analog capability available at every test channel.